Ob im Smartphone, im Hochleistungsrechenzentrum für KI-Anwendungen oder in der Automobilelektronik – ohne Aufbau- und Verbindungstechnik läuft nichts. Electronic Packaging schützt elektronische Komponenten und Sensoren vor Umwelteinflüssen, sichert ihre Funktionsfähigkeit auch unter extremen Bedingungen, ermöglicht höchste Leistungsdichten auf kleinstem Raum und trägt so zu Zuverlässigkeit und Sicherheit in allen Einsatzbereichen bei.

Prof. Dr.-Ing. Ulrike Ganesh, geschäftsführende Institutsleiterin des Fraunhofer IZM, spricht im Interview mit RealIZM über aktuelle Trends und Herausforderungen im Electronic Packaging.

Was sehen Sie als größte technologische Herausforderung?

Prof. Dr.-Ing. Ulrike Ganesh: Historisch ist die Integrationsdichte von Halbleiterbauelementen stark gewachsen, doch dieses Wachstum verlangsamt sich. Wir stoßen an physikalische Grenzen, während die Anforderungen an Leistung, Energieeffizienz und Zuverlässigkeit weiter steigen. Moore’s Law als rein exponentielles Wachstum ist an seine Grenzen gestoßen; dennoch schreiten Innovationen in andere Richtungen voran, insbesondere hin zu 3D- und 2,5D-Architekturen sowie zu neuen Packaging-Konzepten, die Prozessierung, Tests und Packaging integrieren.

Was bedeutet der technologische Trend für die Entwicklung komplexer Hardware-Systeme?

Prof. Dr.-Ing. Ulrike Ganesh: Da Frontend- und Backend-Herstellung enger zusammenwachsen, gewinnen Packaging-getriebene Konzepte wie Chiplet-Architekturen, 2,5D- und 3D-Integration an Bedeutung. Fraunhofer IZM arbeitet daran, solche Ansätze zu optimieren und praktikable Lösungen zu entwickeln, die Skalierbarkeit, Leistungsdichte und Zuverlässigkeit vereinen.

Wie weit ist die 3D-Integration heute in der Halbleiterproduktion marktreif?

Prof. Dr.-Ing. Ulrike Ganesh: 3D-Stacking ist ein zentrales Forschungsthema. Die Machbarkeit einer fehlerfreien Serienproduktion komplexer 3D-Systeme erfordert noch valide Demonstrationen und geeignete Prüf- und Testinfrastrukturen. Erste Teststrukturen existieren; eine marktreife, breit einsetzbare 3D-Packaging-Massenproduktion erfordert weitere Entwicklungen in Prozessierung, Test und Qualifikation.

Welche Bedeutung haben alternative Packaging-Ansätze auf der Technologie-Roadmap?

Prof. Dr.-Ing. Ulrike Ganesh: Jenseits des 3D-Stackings arbeiten wir an 2,5D-Integration, Wafer-Level- und Panel-Level-Packaging. Kreative Kombination etablierter Verfahren mit innovativen Ansätzen eröffnet neue Anwendungsfelder. Ein aktueller Fokus liegt auf Co-Packaged Optics mittels Photonic Wire Bonding.

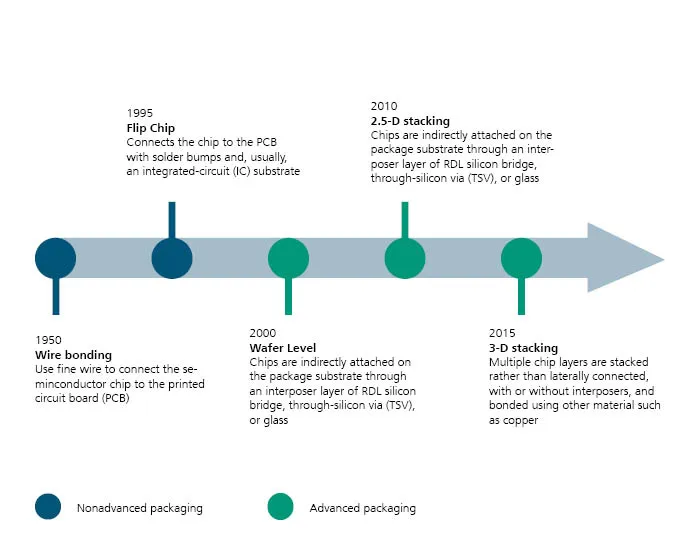

Entwicklungsgeschichte der Verbindungstechnologie (Auszug)

Quellen: Burkacky, O., Advanced Chip Packaging: How Manufacturers can play to win, May 2023, McKinsey Report

Welche Markttrends beobachten Sie derzeit in der Halbleiterbranche?

Prof. Dr.-Ing. Ulrike Ganesh: Die Marktstruktur verschiebt sich: Frontend-Hersteller integrieren vermehrt Packaging-Lösungen in ihr Portfolio. Die Trennung zwischen Chipfertigung (Frontend) und Packaging (Backend) wird aufgebrochen, wodurch neue Kooperationsformen und Wertschöpfung entstehen.

Welche Rolle spielt das Fraunhofer IZM im Zusammenspiel von Chipentwicklung (Frontend) und Packaging (Backend)?

Prof. Dr.-Ing. Ulrike Ganesh: Das Fraunhofer IZM fertigt keine Chips. Wir entwickeln hochgradig anwendungsnahe Electronic-Packaging-Lösungen für Hightech-Halbleiterbauelemente, die es so noch nicht serienmäßig gibt. Gemeinsam mit Industriepartnern arbeiten wir an Advanced Packaging-Techniken für Hochleistungsrechenmodule, die auf fortschrittlichen Knotenarchitekturen basieren. System-Technology-Co-Optimization (STCO) betont die Notwendigkeit einer ganzheitlichen Sicht auf Frontend- und Backend-Aspekte. Diese ganzheitliche Sicht können Sie von uns erwarten.

Wie wird die Weiterentwicklung der Forschungsinfrastruktur sichergestellt?

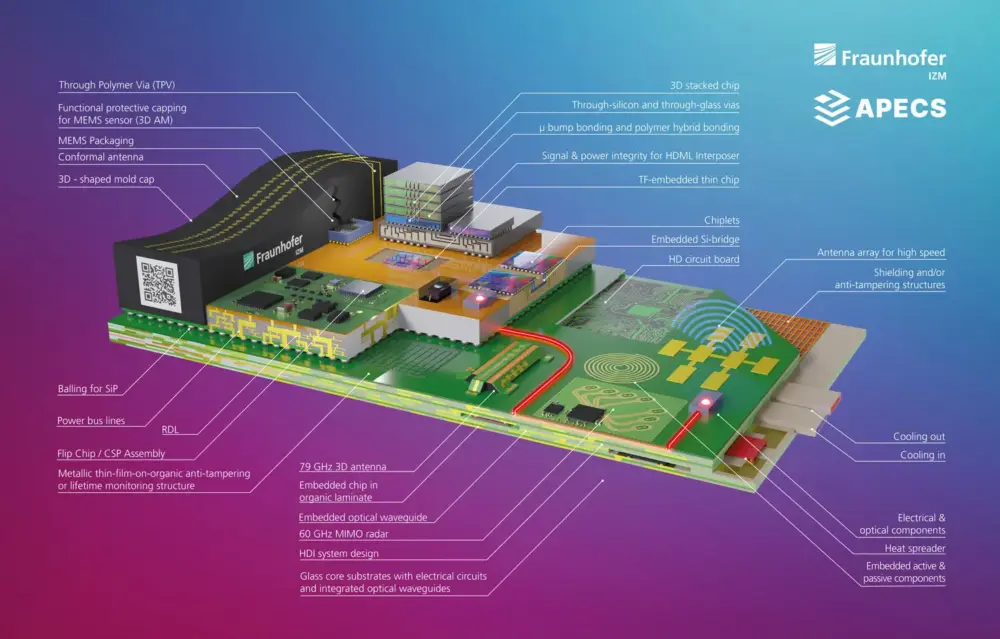

Prof. Dr.-Ing. Ulrike Ganesh: Die APECS-Pilotlinie ermöglicht den hochmodernen Ausbau unserer Infrastruktur. Der neue Gerätepark unterstützt die Anforderungen der kommenden Jahre und erlaubt die Realisierung von Packaging-Strukturen im Submikrometerbereich. Spezifische Maschinen fördern gezielt Entwicklungen in Photonik, Quanten- und neuromorphem Computing, Leistungselektronik und Hochfrequenz. Eine vollständige Ausstattung aller Arbeitsgruppen ist nicht möglich, doch abteilungs- und institutsübergreifende Zusammenarbeit schafft wertvolle Synergien.

Welche Aufgabe hat das Fraunhofer IZM innerhalb der APECS-Pilotlinie?

Prof. Dr.-Ing. Ulrike Ganesh: Als Teil der Fraunhofer-Gesellschaft und der Forschungsfabrik Mikroelektronik Deutschland arbeiten wir eng mit fünf europäischen Pilotlinien zusammen, um rasch passende Kooperationspartner zu identifizieren. In der APECS-Pilotlinie verantwortet das Fraunhofer IZM das Electronic Packaging und gestaltet die zukünftige Technologie-Roadmap maßgeblich mit. In Deutschland sind zwölf Fraunhofer-Institute und zwei Leibniz-Institute an der APECS-Pilotlinie beteiligt. Gemeinsam bündeln wir Kompetenzen und schaffen spürbaren Mehrwert für die europäische Mikroelektronik-Industrie.

Welche Bedeutung haben Nachhaltigkeit und Energieeffizienz im Electronic Packaging?

Prof. Dr.-Ing. Ulrike Ganesh: Seit über 30 Jahren entwickelt unser Institut Elektroniklösungen, die Energie effizient nutzen, Recycling erleichtern und Rohstoffe schonen. Unsere Mitarbeitenden tragen dazu bei, Technologien umweltverträglich und zuverlässig zu gestalten. Mit Unterstützung von KI können wir noch zielgerichteter nachhaltige Elektroniklösungen vorantreiben.

Welche Rolle spielt Advanced Packaging in der für Deutschland wichtigen Automobilindustrie?

Prof. Dr.-Ing. Ulrike Ganesh: Die Automobilbranche geht in Richtung Elektrifizierung. Unsere Packaging-Lösungen für Automotive leisten dazu einen Beitrag, dass E-Antriebe und Leistungselektronik robust und langlebig bleiben. Damit sichern wir technische Zuverlässigkeit und unterstützen zugleich Strukturwandel, Arbeitsplätze und Qualifikationen in Deutschland.

Für welche Anwendungsfelder entwickelt das Fraunhofer IZM aktuell?

Prof. Dr.-Ing. Ulrike Ganesh: Electronic Packaging ist ein breites Innovationsfeld. Wir decken die komplette Prozesskette für Halbleiterbauelemente ab und unterstützen Unternehmen unabhängig von ihrem konkreten Verfahren. Unsere Teams forschen unter anderem in Photonik, Quantencomputing, Luft- und Raumfahrt, Künstlicher Intelligenz, Leistungselektronik und Hochfrequenztechnologie.

Heterogene Integration: High-End Performance Packaging vom Wafer zum System | © Fraunhofer IZM | Mike Groß

Wie sehen Sie die langfristige strategische Ausrichtung des Fraunhofer IZM?

Prof. Dr.-Ing. Ulrike Ganesh: Mittel- bis langfristig prüfen wir, ob wir unsere Expertise breit weiterführen oder uns gezielt auf zukunftsträchtige Technologien fokussieren. Das Spannungsfeld zwischen Vielseitigkeit und Spezialisierung erfordert eine Balance. Am Standort Berlin bearbeiten wir ein breites Spektrum an Materialien und Formaten, entwickeln Prototypen und Kleinserien. Der Dresdner Standort Fraunhofer IZM-ASSID ist stark spezialisiert auf standardisierte Prozesse mit einer 200/300 mm 3D-Wafer-Level-Prozesslinie und auf größeres Produktionsvolumen ausgerichtet.

Vielen Dank für das Gespräch!

Add comment