In dem Forschungsprojekt »CeCaS« entwickelt ein Konsortium unter der Leitung von Infineon Technologies ein innovatives Software-Design-Verfahren und Hardware für High Performance Computing-Anwendungen für zukünftige automobile Steuermodule. Dies umfasst die Entwicklung einer effizienten Methodik für den automatisierten Entwurf von Software für autonomes Fahren.

Eine zentrale Voraussetzung für die Funktionsfähigkeit dieser anspruchsvollen Softwarearchitektur ist der Aufbau und die Zuverlässigkeit der entsprechenden Hardware. Die Arbeitsgruppe »Montage und Verkapselung« am Fraunhofer IZM war für die Realisierung von drei unterschiedlichen Chiplet-Aufbauten auf organischen Schaltungsträgern in diesem Projekt verantwortlich.

Karl-Friedrich Becker, Gruppenleiter »Assembly & Encapsulation Technologies«, und Steve Voges, Prozessentwicklungsingenieur am Fraunhofer IZM, sprachen mit RealIZM über die thermomechanischen Herausforderungen von Chiplet-Modulen für HPC-Anwendungen und Möglichkeiten der Prozessoptimierung.

Chiplets funktionieren nur im Verbund. Ein Chiplet ist ein Baustein, der auf eine bestimmte Fähigkeit spezialisiert ist. Es bildet einen IP-Block und hat eine Kommunikationsschnittstelle, um mit anderen Chiplets zu interagieren. Ein einzelnes Chiplet kann nicht einfach in ein Gehäuse gepackaged werden und selbstständig arbeiten.

»Unsere Aufgabe ist es, die Packaging-Schnittstellen zwischen den Chiplets so zu gestalten, dass eine schnelle und hocheffiziente Kommunikation zwischen den einzelnen IP-Blöcken stattfindet«, beschreibt Karl-Friedrich Becker den Arbeitsschwerpunkt des Fraunhofer IZM in dem Forschungsprojekt »CeCaS«. Die Abkürzung »CeCaS« steht für »Central Car Server«.

Die Forschungsabteilungen von verschiedenen Automobilherstellern und deren Zulieferern arbeiten daher eng mit Unternehmen und Forschungseinrichtungen der Halbleiter-Technologie in verschiedenen Projekten und Verbünden wie beispielsweise dem »Chiplet Center of Excellence (CCoE)« und dem »Automotive Chiplet Program (APC)« zusammen, um die Herausforderungen von High Performance Computing-Anwendungen und Zuverlässigkeitsanforderungen zu managen und um später selbst Chiplet-Module aufbauen zu können.

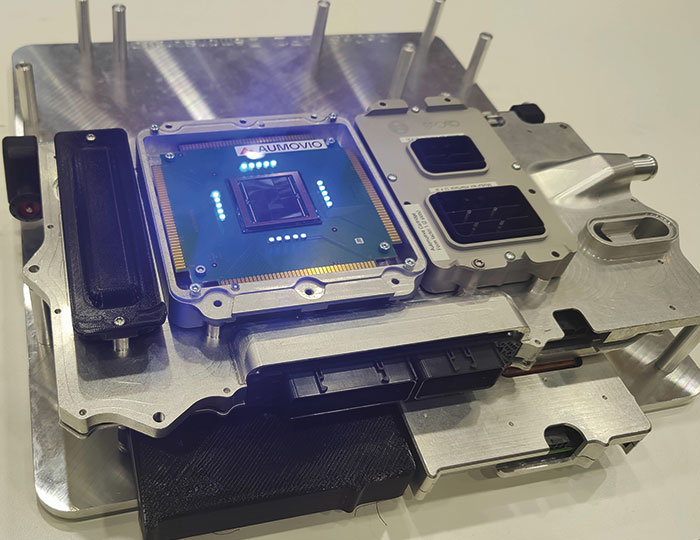

CeCaS-Abschlussmeeting | © CeCaS

Heterogene Integration und Forschungsschwerpunkt des Projektes »CeCaS«

»Die heterogene Integration – das Packaging unterschiedlicher Chiplets aus verschiedenen Fabs auf einer Plattform – ist das zentrale Forschungsthema am Fraunhofer IZM«, erläutert Karl-Friedrich Becker. Im Rahmen des Projektes »CeCaS« haben er und sein Team drei verschiedene Chiplet-Aufbauten auf organischen Schaltungsträgern mittels Flip-Chip-Montage realisiert: »Wir haben Chipgrößen von 10 x 10 mm² bis 40 x 40 mm² Pitches von 300 µm (TTC) bis 150 µm (DC) gepackaged und dabei Siliziumflächen > 1900 mm² pro Package erreicht.«

Die drei Testvehikel dienen dazu, verschiedene Forschungsfragen zu untersuchen. Mit ihrer Hilfe wurden Technologien und Prozesse wie beispielsweise Flip-Chip-Montage, Underfill, Balling und Board-Montage verbessert. Zudem wurden neue Erkenntnisse zu Entwärmungsstrategien und Zuverlässigkeitsmodellen gewonnen.

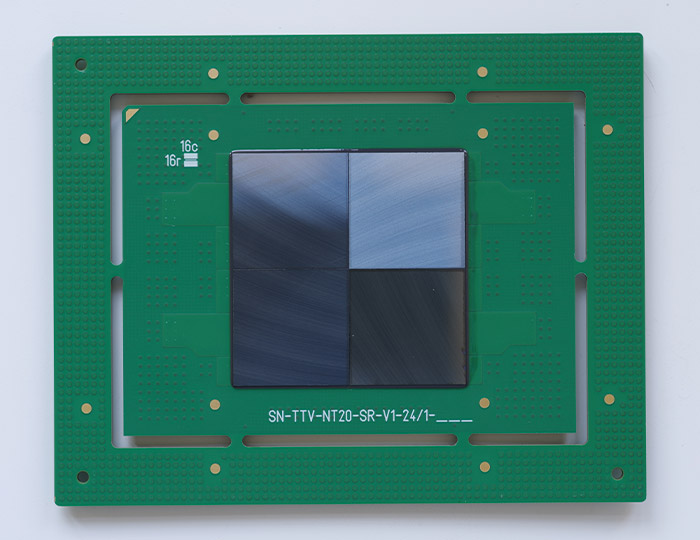

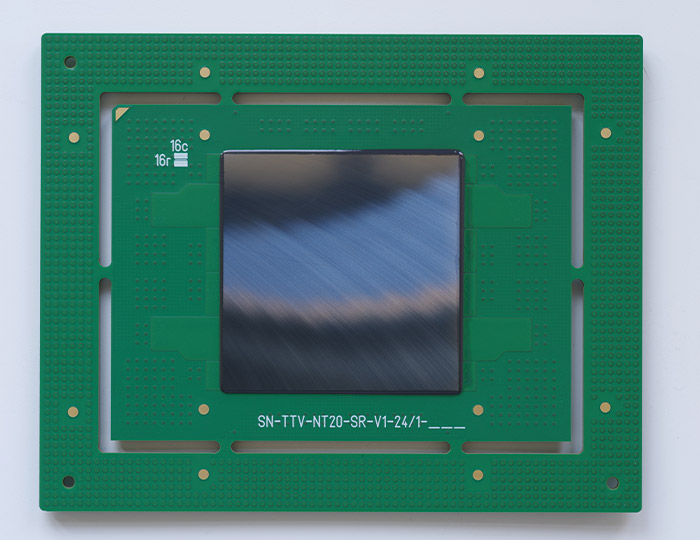

Zuverlässigkeitsbewertung und Testvehikel

Die Bewertung der Zuverlässigkeit des thermischen Testvehikels – mit einer Chipfläche von 40 x 40 mm² und 300 µm Pitch – erfolgte durch das Fraunhofer ENAS auf Basis der Fertigungsdaten und -toleranzen des Fraunhofer IZM. Es gibt sowohl einen monolithischen Aufbau dieses Vehikels als auch einen Aufbau, der aus drei Chiplets besteht. Mit dem Vehikel wurde der Aufbau des Gesamtgehäuses erprobt.

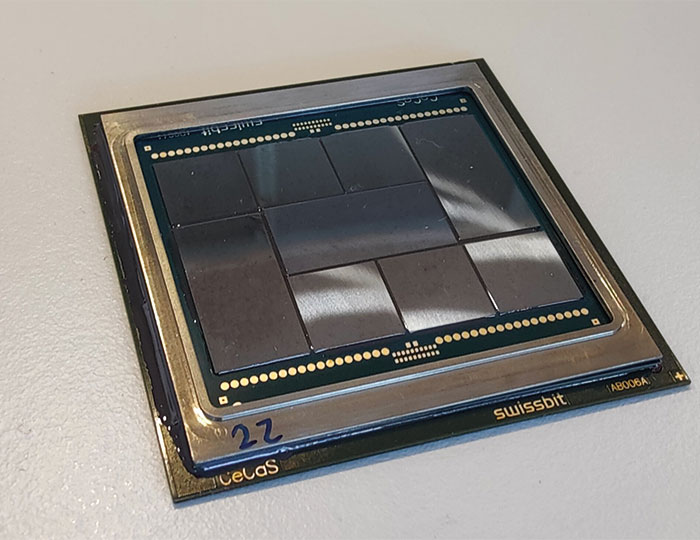

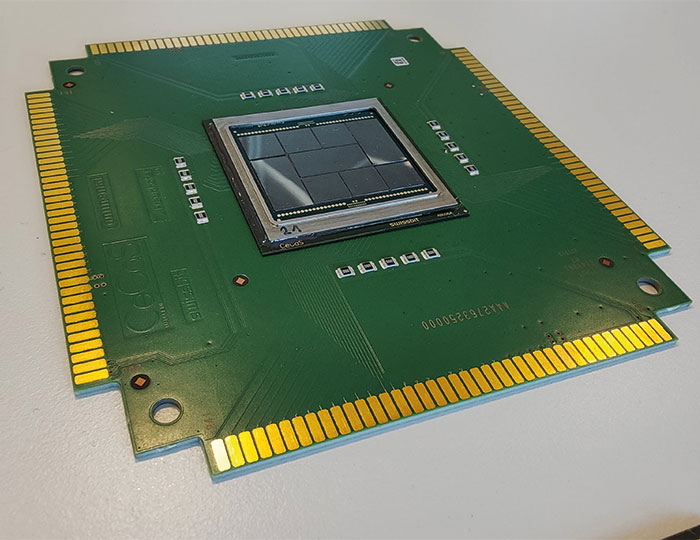

Das elektrische Testboard hat eine Siliziumfläche von 40 x 40 mm² und 150 µm Pitch. Die großflächige Abdeckung der gedünnten Chips auf dem Board hilft, die Fertigungstechnologie kennenzulernen. Auf dem elektrischen Testboard hat der Projektpartner Swissbit ein vorgegebenes Design auf Basis von Netzlisten realisiert. Ziel des Designs war es, Teststrukturen in den unterschiedlichen Ebenen von Chip zu Zwischenträgern/Interposern bis zum Mainboard so zu verbinden, dass im Gesamtaufbau die Kontaktintegrität auf jeder Packaging-Ebene nachgewiesen werden kann.

Die ersten Aufbauversuche dieses komplexen 3D-Aufbaus fanden am Fraunhofer IZM statt, hier wurde die Eingangskontrolle und erste Bestückungsversuche durchgeführt, die Aufbauten analysiert und gewonnenen Erkenntnisse an Swissbit weitergegeben. »Bei diesem Lab-to-Fab-Ansatz konnten wir wichtige Erfahrungen zu Fertigungsketten und den thermo-mechanischen Herausforderungen sammeln, die bei einer großen Chipfläche von 1600 mm² und einem 3-fach Stack – Chip, Interposer und Trägersubstrat – auftreten können«, erläutert Becker.

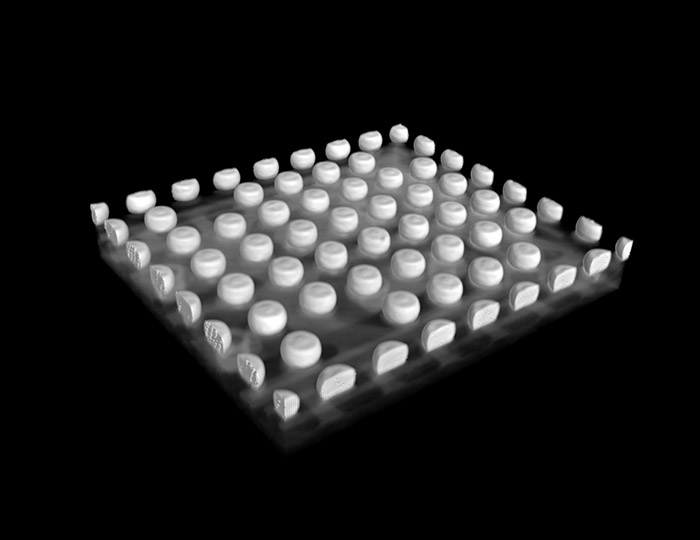

Links: TTV 1 nach Underfill-Setup | © CeCaS

Rechts: TTV 3 nach Underfill-Setup | © CeCaS

Das dritte Testboard mit einer Größe von 70 x 70 mm² enthält unterschiedlich große und unterschiedlich angeordnete Chips. Das Layout der Chips ist an spezifische Applikationen angepasst. Hier wird untersucht, wie die Wärmeleitung nach oben und nach unten am besten gestaltet werden kann.

ETV mit Stiffener und ETV auf Testboard | © CeCaS

Thermomechanische Herausforderungen und Lösungen bei der Flip-Chip-Montage von Chiplets

Steve Voges, Prozessingenieur am Fraunhofer IZM, nennt die Handhabung der großen Chips als eine der Herausforderungen in dem Projekt: »Der Trend der letzten zehn Jahre ging zu immer kleineren und feineren Chips und den dazu passenden Anschlussgrößen. Entsprechend sind auch unsere Maschinen ausgelegt und eingestellt. Jetzt werden die Chips mit sehr feinen Strukturen wieder größer.« Karl-Friedrich Becker fügt hinzu: »Wir arbeiten bereits seit Langem mit großen Flip-Chips. Für uns als Forschende ist es sehr spannend, die Weiterentwicklung unserer Arbeiten zu sehen. Mit dem »CeCaS«-Projekt sind wir einen nächsten wichtigen Evolutionsschritt gegangen.«

Als zweite zentrale Herausforderung sieht Voges die Auswirkung der thermischen Fehlpassung während der Fertigung: Eine Leiterplatte hat einen Ausdehnungskoeffizienten von 18 ppm/K. Der Chip auf der Leiterplatte hat einen Ausdehnungskoeffizienten von 2 ppm/K. Zudem hat der Chip normale Zinn-Silber-Kupfer-Balls. Im Reflow-Ofen wird die Temperatur zunächst auf 260 Grad Celsius hochgefahren und nach kurzer Haltezeit bei 220 Grad Celsius wieder auf Raumtemperatur abgekühlt. Im Ergebnis erstarrt das Lot bei 220 Grad Celsius und bei der weiteren Abkühlung ziehen sich die Materialien gegeneinander zusammen – der Chip nur ein bisschen und das Substrat sehr stark. So kommt es dann zu mechanischen Spannungen im Modul und schlussendlich zu verwölbten Modulen. »In unserer Verantwortung liegt es, die Materialauswahl zu optimieren und die Temperaturführung während dieses Prozesses so zu gestalten, dass der Aufbau sich nur wenig wölbt, wenn er sich abkühlt und Spannungen durch das Zusammenziehen entstehen.«

Effiziente Prozessoptimierung für Automotive-Packages

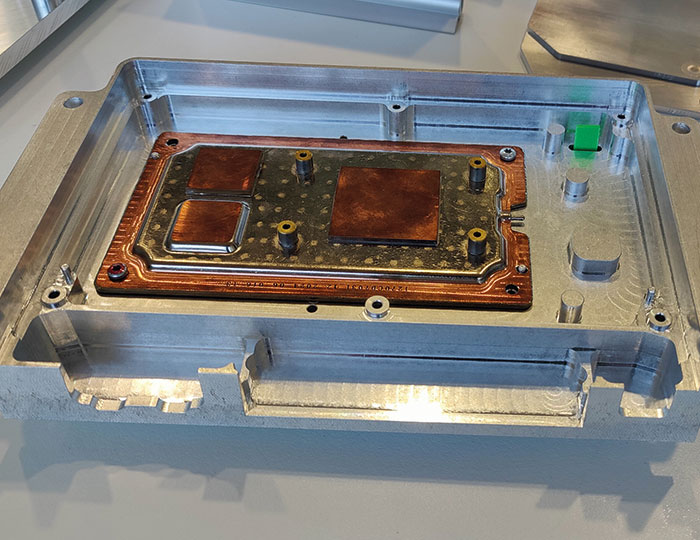

Doch wie stellt man sich ein Automotive-Package am besten vor? Becker beschreibt dies so: »Auf einem Substrat werden Chips montiert. Dieses Substrat mit den Chips wird dann auf ein Trägersubstrat gesetzt. Auf dem Trägersubstrat befinden sich weitere Elektronik, Stromversorgung und Kommunikationsschnittstellen zur Sensorik. Diese bestückte Leiterplatte wird in ein Gehäuse aus Aluminium-Druckguss gesetzt. Dort befinden sich unter anderem die elektrische Kontaktierung (Automotive-Stecker) und der Anschluss für das Kühlwasser. Dieses Package – der Central Car Server – kann dann in ein Fahrzeug eingebaut werden. Wir am Fraunhofer IZM fertigen das Herzstück, das allein nicht funktionieren kann.«

Um dies zu realisieren, haben die Forschenden mit Hilfe von Messtechnik untersucht, was konkret beim Hochskalieren auf größere Chipflächen bei der Flip-Chip-Montage passiert. Zum einen wurde im Voraus festgelegt, was geschehen wird, um die Messtechnik, die bisher für kleinere Aufbauten verwendet wurde, auch für größere Chip-Aufbauten anzupassen und sicherzustellen, dass die Prozesse weiterhin funktionieren. Zum anderen wurde das Profil der Chiplet-Aufbauten nach jedem einzelnen Prozessschritt präzise dreidimensional vermessen, um mögliche Verwölbung(en) zu bestimmen. Mit dem Ansatz der agilen Prozessführungen konnten die Wissenschaftler*innen bei Bedarf die Prozesse sehr schnell anpassen.

Links: TTV 2 auf Testplatine in Kartusche, bereit für den Einbau im Fahrzeug | © CeCaS

Rechts: ETV auf Demomodul | © CeCaS

Karl-Friedrich Becker erklärt dazu: »Wir haben unsere Prozessoptimierung wissensbasiert vorangetrieben, in dem wir mit vielen Zwischenmessungen sehr schnell die Thermomechanik in den Aufbauten bewerten konnten. Trotz der begrenzt verfügbaren Anzahl an Substraten ist es uns gelungen, mit nur wenigen Versuchen in kürzester Zeit sehr große Fortschritte zu erzielen.«

Becker und sein Team erfassen daher für jeden Aufbau einen kompletten Datensatz. Um die komplexe Prozesskette zu verbessern, wurden die Daten der Fertigungsqualität zudem mit den Daten der Produktqualität korreliert. Die Erhebung und Strukturierung der Prozessinformationen sind ein wichtiger Beitrag zum digitalen Zwilling für die Zuverlässigkeitsbewertung.

TTV 1 & 3 3D-Modell-Bump-Array | © CeCaS

Die Expert*innen für Zuverlässigkeitsbewertungen von Elektronik am Fraunhofer IZM verknüpfen die Korrelierung mit Analytik und können somit Aussagen treffen, wie sich die Fertigung auf das Model auswirkt und was das Modell über die zukünftige Zuverlässigkeit und Produktqualität aussagt. Durch die Zustandsbewertung von Elektronik bereits während der Fertigung können wertvolle Informationen zur Zuverlässigkeit und Lebensdauer von elektronischen System-/Baugruppen ermittelt werden.

Schnelle Integration neuer Technologien in Automobilsysteme durch Chiplet-Technologie

»Tauscht man in einem in den Geometrien, Chipgrößen und Materialien qualifizierten System beispielsweise nur die KI-Einheit aus, die aus derselben Fab kommt, eine ähnliche Bumpkonfiguration hat, größere Leistung hat, da sie optimiert wurde, dann spart man viel Requalifikationsaufwand«, fasst Becker die Vorteile von Chiplets für Anwendungen im Automotivebereich zusammen. Dies ermöglicht es, die nächste Generation ohne aufwendige Qualifikation zu nutzen.

Dieser flexible Systemansatz und die Abhängigkeit der Zuverlässigkeit sind von großer Bedeutung, da die Fortschritte und Weiterentwicklungen der verschiedenen Bausteine – beispielweise Rechnereinheit, KI-Einheit und standarisierte Speichereinheit – unterschiedlich schnell verlaufen. Der Chiplet-Ansatz ermöglicht es, wesentliche Teile des Designs gleich zu lassen und bei Bedarf nur einzelne Bausteine auszutauschen. Dies erleichtert die Integration neuer Technologien in bestehende Systeme. Das Projekt »CeCaS« zeigt eindrucksvoll, wie Forschung und Industrie gemeinsam an der Zukunft des Fahrens arbeiten.

»CeCaS«: Supercomputing-Plattform für hochautomatisierte Fahrzeuge

| CeCaS | Die Abkürzung »CeCaS« steht für »Central Car Server«. |

| Laufzeit | 12/2022 – 11/2025 |

| Fördergeber | Bundesministerium für Forschung, Technologie und Raumfahrt (ehemals BMBF) |

| Förderkennzeichen | 16ME0800K |

| Fördersumme | 46,2 Mio. Euro im Rahmen der Forschungsförderrichtlinie MANNHEIM (»Elektronik- und Softwareentwicklungsmethoden für die Digitalisierung der Automobilität«) |

| Koordination | Infineon Technologies |

| Weitere Informationen | Projektwebseite |

| Projektpartner | Ambrosys, AVL Software & Functions, AUMOVIO, Berliner Nanotest und Design, Bosch, CARIAD – Automotive Software for Volkswagen, emmtrix Technologies, FZI Forschungszentrum Informatik, Fraunhofer ENAS, Fraunhofer IMWS, Fraunhofer IPMS, Fraunhofer IZM, Glück Engineering, Hella, Hochschule München, Inchron, KIT Karlsruher Institut für Technologie, Kernkonzept, Missing Link Electronics, STTech, Steinbeis ZFW, Swissbit Deutschland, Technische Universität Chemnitz, Technische Universität München AIR, LIS, SEC, Universität zu Lübeck, ZF Friedrichshafen |

© CeCaS

Add comment