RealIZM-Blog-Serie »Trendthemen der Mikroelektronik« – Teil 1

Warum gilt die Hetero-Integration als Wegbereiter für die nächste Generation der Halbleitertechnik? Im Interview mit RealIZM gibt Erik Jung, Geschäftsfeldentwickler am Fraunhofer IZM, einen Einblick in die Herausforderungen von Halbleiterhersteller*innen und Forschungsinstituten bei der Entwicklung und Fertigung von elektronischen Bauteilen und Systemen mit maximaler Leistung.

Was ist mit Hetero-Integration gemeint?

Erik Jung: Bei der Hetero-Integration werden Halbleiter-Bausteine aus unterschiedlichen Fertigungssträngen z.B. optische, mechanische oder CMOS-Komponenten zusammengefügt, so dass sie – jeweils in ihrer optimierten Fertigung – maximal leistungsfähig sind. Bei der Integration werden die Wege zwischen den einzelnen Funktionseinheiten soweit verkürzt, dass die Signal-Latenzen möglichst gering sind.

In der Vergangenheit wurden unterschiedliche Funktionen der Halbleitertechnik oft in einem – monolithisch genannten- Fertigungsstrang zusammengeführt. So wurden beispielsweise auch Hochfrequenz-Schaltelemente auf einer CMOS-Plattform integriert. Dies mag zwar kostengünstig sein, ist aber nicht optimal für die Funktionalität und Performance. Dieser System-on-Chip (SoC) Ansatz wurde vor allem im Bereich der Mobiltelefone vorangetrieben. Er ist nur dann sinnvoll, wenn die Anforderungen an die Leistungsfähigkeit der Bauelemente und Umgebungsparameter der Komponenten auf einer Fertigungsstrecke realisierbar und die Kompromisse, die man dabei eingeht, für die Funktion nicht entscheidend sind. Dieser Fall wird jedoch immer seltener.

Für eine höhere Sendeintensität müssen z.B. höhere Leistungen über den Hochfrequenzteil abgeführt werden. Dies erfordert eine andere Art der Kühlung. Auch muss auf eine andere Weise Strom zugeführt werden, zum Beispiel von der Rückseite. Das lässt sich jedoch nicht mehr in der CMOS-nahen Technologie als System-on-Chip (SoC) umsetzen.

Worin unterscheiden sich die Begriffe Hetero-Integration und Hetero-Systemintegration?

Erik Jung: Der Unterschied besteht darin, wieviel integriert wird. Bei der Hetero-Integration werden Halbleiter-Komponenten aus unterschiedlichen Prozessen zusammengeführt z.B. ein Bauteil aus der CMOS-Fertigung mit einem VMOS-Halbleiter für die Leistungssteuerung. Bei der Hetero-Systemintegration reicht das bloße Zusammenfügen von Komponenten nicht aus, sondern es wird die ganze Systemfunktionalität mit einbezogen.

Seit wann gibt es das Verfahren der Hetero-Integration?

Erik Jung: Der Begriff Hetero-Integration existiert seit Langem. Größere Aufmerksamkeit erhielt er vor etwa 20 Jahren. Philips hat öffentlichkeitswirksam dargestellt, dass das sogenannte »Moor‘sche Gesetz« irgendwann an seine physikalischen Grenzen gelangen wird und dass mit dem neuen Paradigma »More than Moore« auch in Zukunft erhebliche Verbesserungen in der Leistungsfähigkeit von Systemen möglich sein werden.

1965 formulierte Gordon Moore die Regel, dass sich die Anzahl der Transistoren auf einem Chip und mit ihnen die Rechenleistung etwa alle zwei Jahre verdoppelt.¹ Inzwischen finden sich 100 Milliarden Transistoren auf den modernsten Halbleitern.

Dank stetig neuer Fertigungstechnologieentwicklungen konnte dieser Zeitpunkt immer wieder hinausgeschoben werden. Mit großer Wahrscheinlichkeit werden wir in zirka drei bis fünf Jahren diesen Punkt erreichen. Ein guter Indikator dafür sind die derzeitigen Leistungsparameter von Supercomputern. Es reicht nicht mehr aus, die eingesetzte Chipfläche zu erhöhen, um die Rechenleistung, den Speicherplatz und den Einsatz von Sensorik in Supercomputern weiter auszubauen. Dies gelingt nur durch eine höhere Anzahl an Chips. Daher rückt das Thema der Hetero-Integration zunehmend in den Vordergrund.

Um noch mehr Kommunikation in einem SoC bzw. einem CMOS-System zu ermöglichen, brauchen wir ein Verfahren, das über die Vorhersage von Moore hinausgeht: »More than Moore«“. In einem Nebensatz zu seiner berühmten Regel verwies der Ingenieur Gordon Moore bereits darauf, dass es sich als wirtschaftlicher erweisen kann, große Systeme aus kleineren Funktionen aufzubauen, die separat hergestellt und schließlich miteinander verbunden sind. Hier hat also der Namensgeber bereits weitergedacht, als Generationen von Halbleiteringenieuren nach ihm. Für uns heißt das, wir müssen uns jetzt verstärkt auf die heterogene Integration fokussieren.

Welche Anwendungsbereiche profitieren Ihrer Meinung nach am meisten von der heterogenen Integration?

Erik Jung: Globalwirtschaftlich betrachtet spielt Hetero-Integration überall eine Rolle: im High-Performance Computing, in der Medizintechnik, in der Mobilität, bei den Erneuerbaren Energien, im Smart Farming. In diesen Bereichen kommt Hetero-Integration in sehr unterschiedlicher Ausprägung zum Einsatz. Je nach Einsatzbereich werden spezifische Verfahren verwendet und sehr unterschiedliche Kostenziele verfolgt.

Wichtig zu verstehen ist, dass eine Sensorik-Anwendung für den Einsatz im »Internet der Dinge« anders von ihren Komponenten aufgesetzt ist als eine Automotive-Anwendung für das Autonome Fahren oder im Bereich des High-Performance Computing für das Training großer Sprachmodelle mit Hilfe Künstlicher Intelligenz.

Welche technologischen Verfahren stehen bei der Hetero-Integration zur Verfügung?

Erik Jung: Hetero-Integration stellt man sich am besten als einen mächtigen Technologie-Baukasten vor. Ähnlich wie bei einem Schweizer Taschenmesser stehen diverse exzellente Werkzeuge – in unserem Fall technologische Verfahren – zur Verfügung. Je nach Anwendung wird das passende Technologieset ausgewählt. In Vorstudien wird speziell für den jeweiligen Anwendungsfall ausgearbeitet, welche Verfahren am besten geeignet sind, z.B. das Fan-Out-Packaging oder die quasi-monolithische Integration.

Um die richtige Auswahl treffen zu können, müssen die Herausforderungen des jeweiligen Anwendungsfalls berücksichtigt und die Frage nach dem Mehrwert für die Kund*innen und Nutzer*innen geklärt werden. Für einige Anwendungen hat sich bereits herauskristallisiert, welche Werkzeugsets für welche Komponenten passend sind. Für anderer Einsatzbereiche sind wir noch in der Findungsphase.

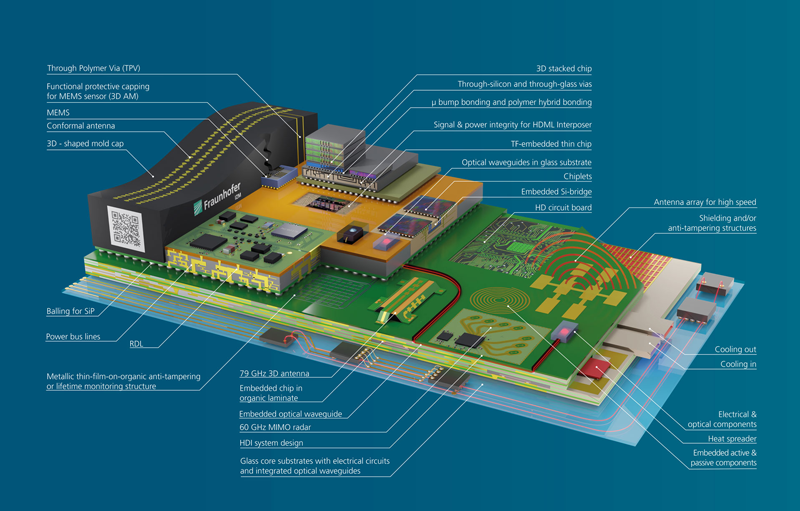

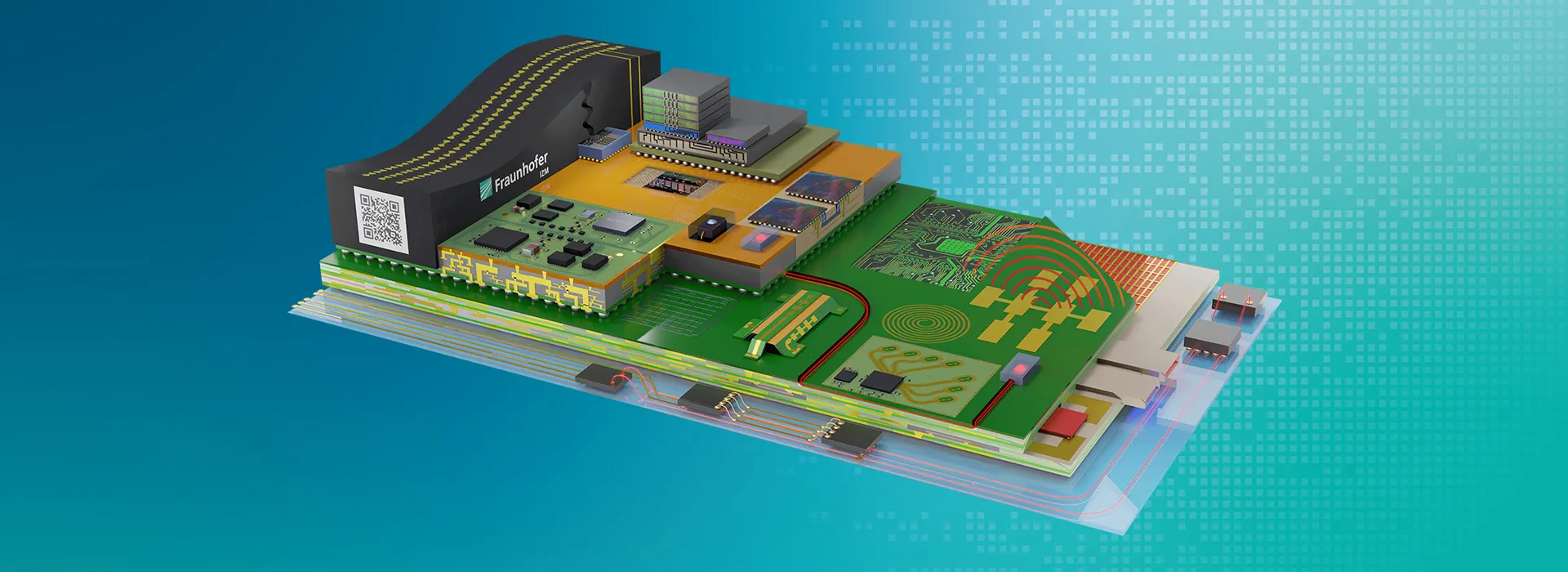

Auf dem Titelbild der Institutsbroschüre des Fraunhofer IZM ist das Technologie-Portfolio des Hauses im High-End Performance Packaging zu sehen. Inwiefern visualisiert dieses Bild das Thema Hetero-Integration?

Vision der Hetero-Integration am Beispiel des High-End Performance Packaging, | © Fraunhofer IZM

Erik Jung: Die Grafik zeigt unsere Vision der Hetero-Integration am Beispiel des High-End Performance Packaging und präsentiert den Technologie-Werkzeugkasten, der zur Realisierung der Hetero-Integration an unserem Forschungsinstitut zur Verfügung steht. Bei der Entwicklung dieser Abbildung haben wir alle Abteilungs- und Gruppenleiter*innen intern befragt, welche Themen ihrer Meinung nach die heterogene Integration ausmachen.

Im Ergebnis sehen wir, dass die heterogene Integration ein unglaublich mächtiges Verfahren ist, um mit vielfältigen Herangehensweisen ein System miniaturisiert aufzubauen. Die Hetero-Integration umfasst ein großes Technologie-Portfolio über die verschiedenen Package-Levels, die sich gegenüber den letzten 30 Jahren in Richtung des Chips verschoben haben:

- Level 0 ist der Chip,

- Level 1 ist hier nunmehr die Integration der Chips auf einen Wafer oder das Stapeln der Chips übereinander,

- Level 2 ist die Integrationslage mit organischen Interposern oder Glasinterposern mit den Anschlüssen für die späteren Systemkomponenten,

- Level 3 ist das Substrat als Systemträger mit erweiterten Funktionalitäten.

Diese im Bild dargestellte Form des Werkzeugkastens würden wir unseren Kund*innen nicht anbieten. Das wäre eine eierlegende Wollmilchsau. Im Auftrag unserer Kund*innen analysieren wir für den spezifischen Anwendungsfall, welche Technologien passend und zielführend sind z.B. 3D-Stapel-Integration, die Leiterplatten-Integration oder die Glas-Interposer-Integration.

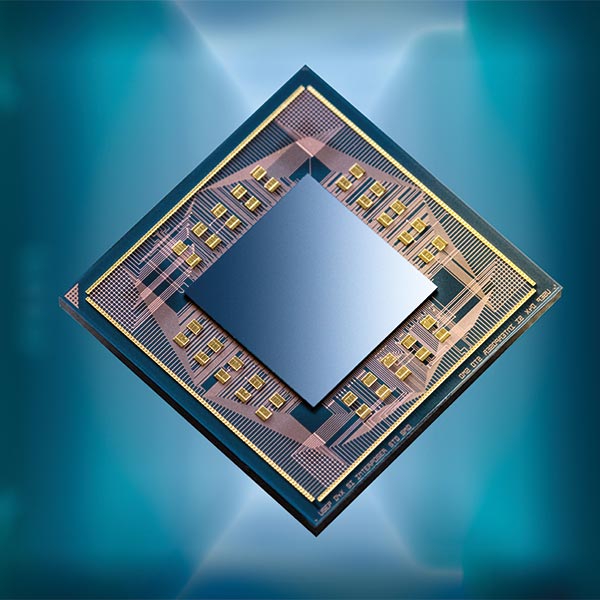

Links: Beispiel für Level 1-Integration: Testinterposer für Design-/ Funktionsverifizierung des im Projekt USeP entwickelten Risc-V Prozessors in 22FDX® Technologie © Fraunhofer IZM I Volker Mai

Mitte: Beispiel für Level 1-Integration © Fraunhofer IZM I Volker Mai

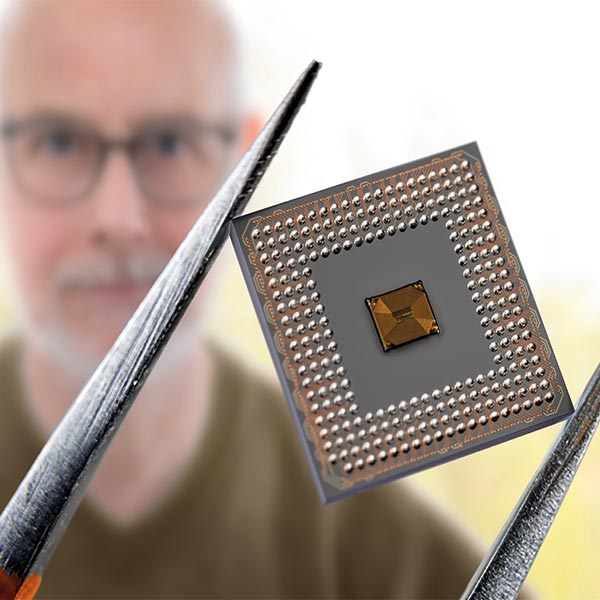

Rechts: Glas-Interposer: Hermetisch dichtes Glaspackage für HF-Anwendungen mit TGVs & integriertem ASIC © Fraunhofer IZM I Volker Mai

Es gibt demnach nicht das eine Verfahren der Hetero-Integration, welches sich für alle Anwendungen nutzen lässt?

Erik Jung: Es wird derzeit versucht, Technologien über eine gewisse Reifezeit zu konsolidieren. Möglicherweise sind technologische Ansätze, die wir heute präferieren, in drei Jahren obsolet.

Nehmen wir zum Beispiel das Hybrid Bonden: Mit dieser Fügetechnik lassen sich moderne Chips wie eine GPU oder eine TPU mit Stapeln von Speicherchip in kleinsten Kontaktrastern von wenigen Mikrometern zusammenführen. Würde man dieses Verfahren auf eine medizinische Anwendung übertragen, kommt man zu dem Schluss, dass eine derartige Leistungsbündelung mit damit einhergehenden Kosten gar nicht notwendig ist. Statt des Hybrid-Bondens wäre die Fan-Out-Systemintegration oder Mikrobump-Integration vorzuziehen, da diese Verfahren kostengünstiger und weniger aufwändig in Hinblick auf den Infrastrukturbedarf sind.

Verstehe ich das richtig, dass Forschungsinstitute wie das Fraunhofer IZM Technologie-Werkzeugkästen auf dem neuesten Stand für Industriepartner*innen vorhalten?

Erik Jung: Das ist genau richtig. Mit den verschiedenen Pilotlinien, die derzeit in Europa aufgebaut werden bzw. sich in der Planung befinden, ist es möglich, den kompletten Technologie-Werkzeugkasten vorzuhalten. Doch damit allein ist es nicht getan. Zum einen muss man das Systemdesign verstehen. Zum anderen muss man den riesigen Technologie-Werkzeugkasten sehr gut kennen, um die richtigen Designentscheidungen für die vielfältigen Anwendungen treffen zu können. Nur im Schulterschluss mit den Partnerinstituten im Forschungsverbund Forschungsfabrik Mikroelektronik Deutschland (FMD) und den europäischen Kooperationspartnern können wir das leisten. Im Verbund sind wir stark.

Es gibt ausgewiesene Design-Institute, die beispielsweise auf unsere Expertise beim Packaging und der Zuverlässigkeitsbewertung zurückgreifen. Ein substanzieller Teil des IZM-Werkzeugsets sind zudem die Zuverlässigkeitstests. Häufig wird nur elektrisch getestet. Bei Sensorik, Aktorik oder RF-Kommunikationsschnittstellen müssen auch genau diese funktionalen Aspekte getestet werden. Nur so lässt sich nachvollziehen, warum diese ausfallen. In diesem Bereich ist das Fraunhofer IZM sehr gut aufgestellt. Gehen Anforderungen darüber hinaus, arbeiten wir mit unseren Verbundpartnern zusammen.

Seit wann beschäftigt sich das Fraunhofer IZM mit Hetero-Integration?

Erik Jung: Seit der Gründung unseres Forschungsinstituts 1993 beschäftigen wir uns mit Mikrointegration und mit Zuverlässigkeit. Genau hierfür stehen das »M« und das »Z« im Institutsnamen. Verschiedenste Halbleiter-Bauelemente in kleinstmöglicher Form zuverlässig zusammenzuführen, ist Teil unser Forschungs- und Entwicklungs-DNA. Was sich für uns über die Jahre gewandelt hat, ist mit einer größeren Materialvielfalt zu arbeiten.

Werden Entwicklungen heute von der Technologie oder von der Anwendung vorangetrieben?

Erik Jung: Früher wurden Technologien bis zu einem bestimmten Reifegrad entwickelt und von der Industrie aufgegriffen. Wir beobachten, dass durch eine zunehmende Nachfrage auf Seiten der Anwender*innen die technische Notwendigkeit bestimmte Entwicklungen zu forcieren, viel stärker als früher akzeptiert wird. Der Markt treibt die technologische Entwicklung zunehmend voran.

Dies lässt sich besonders auch bei der Entwicklung der 3D-Stapeltechnologien beobachten. Noch vor wenigen Jahren hat man die schon mehrere Dekaden zurückliegenden Technologieentwicklungen hierzu in den hintersten Schubladen versteckt. Erst durch die Entwicklung im Bereich der künstlichen Intelligenz wurde daraus ein regelrechter Hype.

Wie wirkt sich diese Entwicklung auf Halbleiter-Hersteller und Forschungsinstitute aus?

Erik Jung: Für uns als Forschungseinrichtung ändert sich die Orientierung auf der technologischen Seite. Bisher konnten wir mit Geräteparks arbeiten, die zwei oder drei Generationen der am Markt gängigen Halbleitertechnik zurückstanden. Inzwischen sind die Anforderungen jedoch so hoch, dass wir zunehmend in die Halbleiterreinräume hineingehen. Für uns im Forschungs- und Entwicklungsbereich und auch für die Halbleiterhersteller bedeutet das höhere Kosten und stetige Investition in die technologische Infrastruktur. Alle paar Jahre müssen neue Fabs aufgesetzt bzw. Labore neu ausgestattet werden.

Die neueste Gerätegeneration ist inzwischen so teuer und die Anforderungen an die Systemperformance so hoch, dass das Mithalten für alle Akteur*innen zu einer echten Herausforderung wird. Einige der Halbleiter-Hersteller setzen daher auf Fabs ausschließlich für das Packaging. Das, was früher High-End in der Frontend-Technologie war, ist ins Backend gerutscht.

Hinzukommt, dass für die Weiterentwicklung der Integrationstechnologien die vorhandene Infrastruktur älterer Fabs genutzt wird, jedoch andere Produktansätze gewählt werden. Beispielsweise werden dort keine funktionalen CMOS-Strukturen mehr gefertigt, die nach heutigem Stand der Technik auf diesen Fertigungsstrecken obsolet wären, sondern nur noch es werden hochdichte Verbindungselemente, die sogenannte Interposer, strukturiert.

Lässt sich damit der Fab-Boom in Großraum Sachsen und in Magdeburg erklären? Sind diese Fabs nicht bereits überholt, bevor sie in Betrieb gehen werden?

Erik Jung: Die Hetero-Integration hat mit dem Fab-Boom relativ wenig zu tun. Dieser hängt vielmehr mit der Globalisierung und den Herausforderungen der Lieferketten und lokalen regulatorischen Randbedingungen zusammen. So macht es Sinn, die Produktion an die Märkte und den Bedarf dichter heranzuführen.

Welche Rolle spielen die Themen Nachhaltigkeit und Hardwaresicherheit bei der Hetero-Integration?

Erik Jung: Die Grundidee bei der Hetero-Integration ist, das Beste für Performanz und Effizienz herauszuholen und dabei entsprechend die Kosten und ökologischen Auswirkungen des Gesamtsystems so gering wie möglich zu halten. Die Notwendigkeit, den ökologischen Fußabdruck von Technologien beziffern zu können, nimmt zu und wird immer mehr Bestandteil unserer Arbeit.

In dem Forschungsprojekt Green ICT untersuchen wir beispielsweise die ökologischen Randbedingungen von Informations- und Kommunikationstechnik-Infrastrukturen. Ziel des Projekts ist es, den Ressourcen- und Energieverbrauch bei der Halbleiter-Herstellung von der Auswahl der Rohstoffe für die Herstellung des Halbleiter-Substrats über das Chip- und Leiterplatten-Design bis hin zum Routing und der Board-Integration zu optimieren.

In Bezug auf Hardwaresicherheit bietet die Hetero-Integration den Vorteil, in die aufgeteilten Funktionalitäten Sicherheits-Features und Anti-Tampering-Features einzubringen sowie durch die verteilte Fertigung auch Single Points of Failure in der sicherheitsrelevanten Fertigungskette zu vermeiden.

Eingebetteter Mikro-RFID-Tag in der Umverdrahtung eines Chips zur Komponentenidentifikation und Sicherstellung vertrauenswürdiger Lieferketten | © Fraunhofer IZM I Volker Mai

Das Fraunhofer IZM ist an mehreren ZEUS-Forschungsprojekten der Initiative »Vertrauenswürdige Elektronik« des Bundesministeriums für Bildung und Forschung beteiligt.

Vielen Dank für das Gespräch!

¹ G. E. Moore: Cramming more components onto integrated circuits. In: Electronics. Band 38, Nr. 8, 1965, S. 114–117 (stanford.edu [PDF]).

Add comment