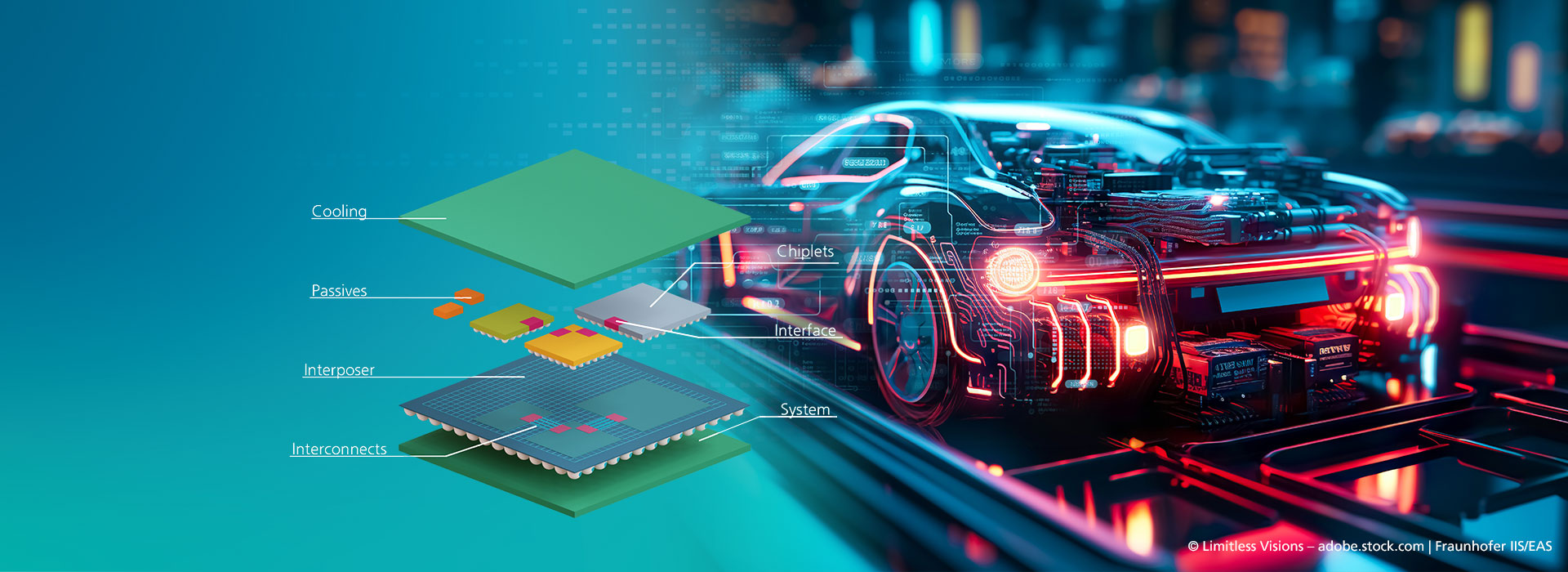

RealIZM-Blog-Serie »Trendthemen der Mikroelektronik« – Teil 2

Mit dem neu gegründeten Chiplet Center of Excellence (CCoE) in Dresden wollen Fraunhofer IIS/EAS, Fraunhofer IZM und Fraunhofer ENAS neue Maßstäbe für die Automobil-Elektronik setzen. Dr. Michael Schiffer, Leiter der Abteilung »Wafer Level System Integration«, und Dr. Andreas Ostmann, Leiter der Abteilung »System Integration und Interconnection Technologies«, sprachen mit RealIZM über die Notwendigkeit, innovative Chiplet-Lösungen zu entwickeln und die heterogene Integration sowie das Electronic-Packaging in Europa voranzutreiben.

Zu Beginn: Können Sie uns bitte erklären, was Chiplets sind?

Dr. Michael Schiffer: »Chiplets« sind in erster Linie eine Design-Philosophie. Die Architektur von Chiplets beruht auf dem Konzept, elektronische Bauelemente unterschiedlicher Größe und Funktionsweisen sowohl neben- als auch übereinander zusammenzufügen – ähnlich dem Lego-Prinzip. Als Verbindungselemente dienen hauchdünne Drähte. Im Ergebnis bilden die Chip-Bausteine ein funktionsfähiges Gesamtsystem – ein sogenanntes »System-on-Chip« (SoC). Im Unterschied zu einem »Multi-Chip-Modul«, bei dem die verschiedenen Chips auch eigenständig funktionieren, ist ein einzelnes Chiplet nur bedingt in sich funktionsfähig.

Eine Standarddefinition für »Chiplet« gibt es bisher noch nicht. In Forschungskreisen werden zwei Ansätze unterschieden:

1. Die einzelnen IP-Blöcke eines SoCs werden zerlegt, als einzelne Chiplets in ein heterointegriertes System eingebracht und sichergestellt, dass die einzelnen Blöcke miteinander kommunizieren.

2. Zwei SoCs von unterschiedlichen Herstellern werden über eine Brücke miteinander zu einem Chiplet-System zu verbunden.

Welche Vorteile und Herausforderungen gehen mit der Entwicklung von Chiplet-Systemen einher?

Dr. Michael Schiffer: Der Chiplet-Ansatz bietet beispielsweise große Vorteile in Bezug auf die Hardwaresicherheit und die vertrauenswürdige Elektronik. Nur derjenige, der den Entwurf des gesamten Chiplet-Systems verantwortet, hat auch die Sicht auf alle Komponenten. Das heißt innerhalb der verteilten Lieferkette kann nur der eigene Chip kopiert werden. Das Kopieren des gesamten Systems wird für Außenstehende erschwert. Zukünftig können noch weitere Sicherheitsfunktionen durch photonische Teilkomponenten hinzukommen.

Dr. Andreas Ostmann: Die Umsetzung von Chiplet-Systemen ist sehr anspruchsvoll. Die Bauelemente müssen elektrisch so eng miteinander gekoppelt werden, dass sie sich zusammen wie ein Siliziumchip verhalten. Die Herausforderung für uns als Technologen besteht darin, kurze und schnelle Verbindungen mit möglichst wenigen Verlusten zwischen den elektrischen Bauteilen sicherzustellen.

Welche Verbindungstechnologie eignen sich Ihrer Meinung nach am besten für Chiplets?

Dr. Andreas Ostmann: Für Chiplet-Systeme wird derzeit meist die Flip-Chip-Montage eingesetzt. Für KI-Systeme mit sehr hoher Rechenleistung gibt es aber auch schon eine 3D-Montage, bei der die einzelnen Chiplets direkt übereinandergestapelt werden.

Chiplets besitzen ein großes Potenzial für die Halbleiterindustrie. In welchen Anwendungen kommen Chiplets bereits zum Einsatz?

Dr. Michael Schiffer: Chiplets kommen bereits in Servern großer Rechenzentren zum Einsatz, um riesige Datenmengen zu verarbeiten. Die Kosten pro Chiplet-Subsystem für Server sind jedoch 5-stellig. Hinzukommt, es handelt sich um geschlossene Öko-Systeme, da große Unternehmen (AMD, Intel, Nvidia, Apple und Google) diese Systeme entwickeln. Nur große Unternehmen können es sich leisten, Architekturen mit proprietären Technologien zu entwickeln.

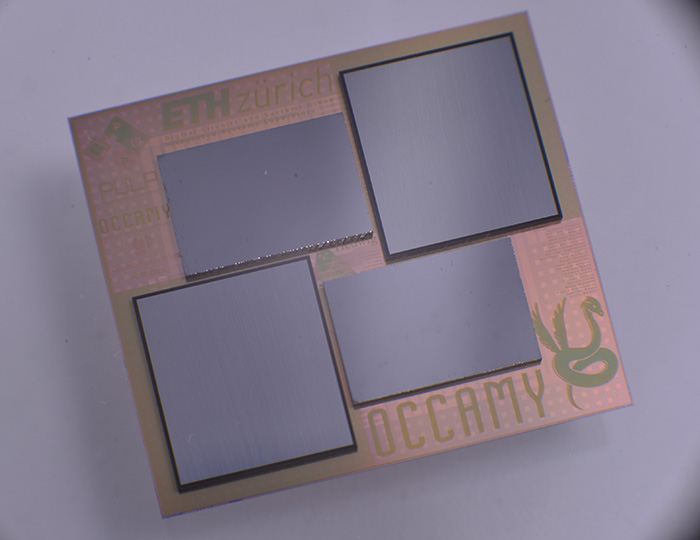

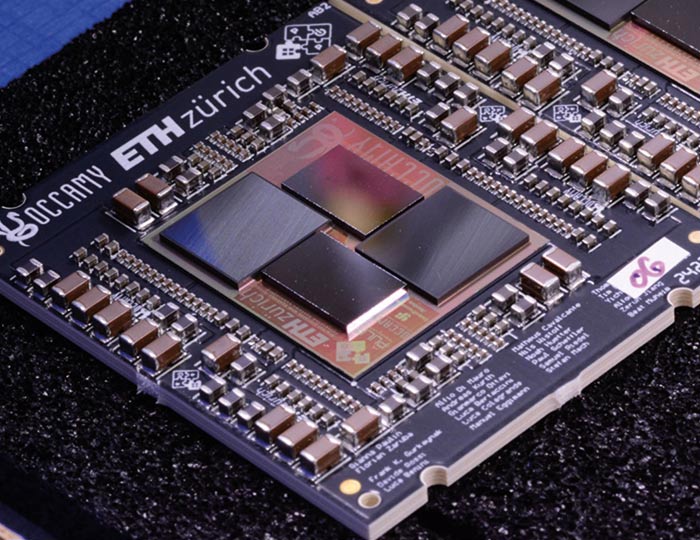

Links: Si-Interposer mit zwei Accelerator Compute Units und zwei High Bandwidth Memory (HBM) Stacks für High Performance Computing. Chip- und Systemdesign: ETH Zürich. Interposer-Finish und Chip-Montage: Fraunhofer IZM. | © ETA Zürich | Fraunhofer IZM

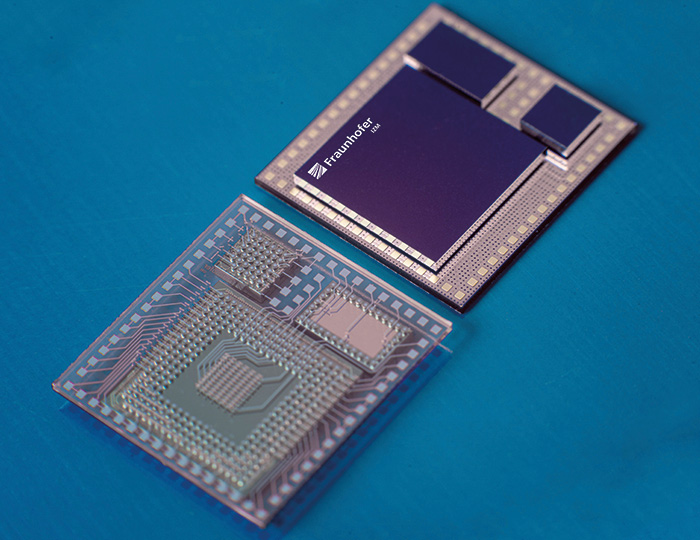

Mitte: Glas-Interposer mit TGVs und montierten Testchiplets | © Fraunhofer IZM

Rechts: KI-Chip mit High Bandwidth Memory montiert auf Si-Interposer und Trägerleiterplatte | © Fraunhofer IZM

Können Sie uns mehr über das Chiplet Center of Excellence (CCoE) erzählen, das vom Fraunhofer IZM zusammen mit anderen Fraunhofer-Instituten initiiert wurde? Welche Anwendungen stehen dabei im Fokus?

Dr. Michael Schiffer: Gemeinsam mit dem Fraunhofer IIS/EAS und Fraunhofer ENAS hat das Fraunhofer IZM mit dem Institutsteil Fraunhofer IZM-ASSID in Dresden eine zukunftsweisende Forschungsinitiative gestartet. Das Chiplet Center of Excellence (CCoE) fokussiert sich auf Anwendungen aus der Automobil-Elektronik. Hierbei wird der komplette Designflow, von der Systemsimulation bis zum Demonstrator angewendet und auf etwaige Gaps hin analysiert.

Dr. Andreas Ostmann: Ein Ziel ist, verschiedene Chiplet-Lösungen in Bezug auf ihre Leistungsfähigkeit, Kosten und Zuverlässigkeit zu bewerten. Zugleich sehen wir darin auch eine große Chance, unsere Forschungs- und Entwicklungsarbeiten bei der Heterogenen Integration und dem Electronic-Packaging in Europa voranzutreiben.

Welche praktischen Vorteile bieten Chiplet-Systeme für die Automobilhersteller im Vergleich zu herkömmlichen Mikrochip-Systemen?

Dr. Michael Schiffer: Aus meiner Sicht gibt es drei Gründe, warum sich Chiplet-Systeme für die Automobilindustrie eignen. Erstens erfordert die Komplexität elektronischer Systeme für das autonome Fahren extreme hohe Rechenleistungen. Zweitens sind in diesem Industriezweig die verteilten Lieferketten bereits etabliert. Das heißt der Central Control Chip, der alles miteinander verbindet, kommt mit großer Wahrscheinlichkeit von dem jeweiligen Automobilhersteller.

Drittens ist die Entwicklung von Chiplet-Systemen kostengetrieben. Um wettbewerbsfähig zu sein, müssen die Kosten bezahlbar sein. Die Designkosten für einen 7 nm Chip belaufen sich derzeit auf etwa 300 Mio. US-Dollar. Die Kosten für die Entwicklung eines Gesamtsystems können je nach Anzahl der Chiplets bis zu 500 Mio. US-Dollar oder mehr kosten. Diese Investition kann sich kein einzelnes Unternehmen mehr leisten.

Laut Prognose des indischen Marktforschungsinstituts Prudour wird der europäische Chiplet-Markt von 0,697 Mrd. US-Dollar (2023) auf voraussichtlich 54,612 Mrd. US-Dollar in 2033 wachsen. Die jährliche Wachstumsrate (CAGR) beträgt im Prognosezeitraum 50,3%.

Vor allem der Automotive-Bereich wird die Marktexpansion vorantreiben. Fortschrittliche Fahrerassistenzsysteme (ADAS), Elektrofahrzeugen (EVs) und Technologien für vernetzte Autos erfordern leistungsstarke und energieeffiziente Halbleiterlösungen. Nach Angaben des Europäischen Verbands der Automobilzulieferer (CLEPA) ist der Automobilsektor für 37 % der Gesamtnachfrage nach Halbleitern in Europa verantwortlich.1

Das heißt, Standards sind für die Zukunft der Chiplet-Technologie wichtig?

Dr. Andreas Ostmann: Um wie eingangs beschrieben die Vision eines Lego-Baukastens für Chiplets realisieren zu können, sind Standards mittel- bis langfristig erforderlich. Es gibt Konsortien, die sich um diese Stanardisierung kümmern, wie beispielsweise Universal Chiplet Interconnect Express (UCIe) und Bunch of Wires (BoW).

Dr. Michael Schiffer: Der Bedarf an offenen Standardlösungen und Schnittstellen, die es ermöglichen, dass verschiedene Chips miteinander kommunizieren, ist sehr groß. Mit unserer Expertise in der Aufbau- und Verbindungstechnologie wird das CCoE innovative Maßstäbe für Chiplet-Lösungen für die Automobilbranche setzen.

Wie kann das Chiplet Center of Excellence (CCoE) zur Entwicklung offener Standardlösungen für Chiplet-Systeme beitragen?

Dr. Andreas Ostmann: Salopp formuliert, schauen wir über den Chiprand hinaus, um die Interoperabilität am Chiplet-Markt zu ermöglichen. Beim Thema Automotive kommt erschwerend hinzu, dass für die Interoperabilität auch Redundanzleitungen erforderlich sein werden.

Dr. Michael Schiffer: Beim CCoE sehen wir in der engen Zusammenarbeit mit Designern einen großen Mehrwert. Zu Beginn widmen wir uns zunächst technologischen, desginunterstützenden und messtechnischen Themen. Sowohl auf der Leiterplatte als auch auf der Wafer-Ebene haben wir eine Vielfalt an Designs, die im Anschluss vom Fraunhofer IIS/EAS gemessen werden. Unsere Vision ist, langfristig für das Package für die Verbindungen zwischen den Chips verifizierte Design-Regeln aufzustellen. Ein Ziel des CCoE ist die Entwicklung eines Package-Assembly-Design-Kits (PADK), um dieses in einer Design-Umgebung zu implementieren.

An welche Zielgruppen richtet sich das Angebot des CCoE?

Dr. Andreas Ostmann: Das CCoE richtet sich sowohl an Automobilhersteller (OEMs) und deren Zulieferer (Tier 1) über Chiphersteller und Halbleiterproduzenten bis hin zu Design-Software-Entwicklern (EDA Tools). Im ersten Schritt erproben wir die Design-Umgebung. Diese ist enorm wichtig, um vom Halbleiter bis hin zu den letzten Verbindungen unten, den Bumps und Schnittstellen zur Außenwelt alles in einem Guss zu simulieren, zu entwickeln und zu entwerfen.

Welche weitere Expertise bringt das Fraunhofer IZM in das CCoE ein?

Dr. Andreas Ostmann: Das Fraunhofer IZM unterstützt Unternehmen, bezahlbare Chiplet-Systeme aufzubauen und für den jeweiligen Anwendungsfall die passende Verbindungstechnik, Systematik und Datenübertragung zwischen den einzelnen Elementen zu identifizieren. Um auf die Metapher mit den Lego-Bausteinen nochmals zurückzukommen: Wir entwickeln die Steckverbindungen – die Noppen.

Die Hetero-Integration ermöglicht uns eine größere Flexibilität und Skalierbarkeit beim Halbleiterdesign. Die flexible Herangehensweise erlaubt es uns, Prototypen schnell zu entwickeln und iterative Designprozesse zu verfolgen, was unseren Kunden eine zügigere Markteinführung ermöglicht. Wir erarbeiten maßgeschneiderte Lösungen, mit dem Ziel für jeden Einsatzbereich das Beste für die Performance und Kosten rauszuholen und transferieren unser Technologiewissen an die Industrie. Das ist einer der Grundgedanken von Fraunhofer. Wir verstehen uns als Enabler auf Systemebene und unterstützen neue Ideen zu Chiplet-Systemen.

Dr. Michael Schiffer: Als Experten für Interfaces bieten wir vielfältige technologische Lösungen an – von High-End Technologien wie dem Hybridbonden am Fraunhofer IZM-ASSID in Dresden über waferbasierte Lösungen mit Interconnects mit Feinstpitch im unteren µm-Bereich bis hin zu preiswerteren Ansätzen auf Substratebene. Dank unseres großen Technologie-Portfolios können wir beim Aufbau von Chiplet-Systemen elektronische Bausteine unterschiedlicher Funktionen, Größen und Prozesstechnologien mischen und anpassen, vom Silizium bis zum Board haben wir die Expertise im Haus versammelt und das ist einzigartig bei Fraunhofer.

Welcher Faktor beeinflusst die Auswahl der Komponenten maßgeblich?

Dr. Michael Schiffer: Die Kosten für ein Chiplet-System im Automotive-Bereich müssen pro Package im unteren zweistelligen €-Bereich liegen. Interposer aus Silizium wären daher nicht die richtige Wahl. Für uns heißt es zu prüfen, wo wird tatsächlich hohe Leistung benötigt und mit welcher Technologie kann diese kostenoptimiert umgesetzt werden.

Wie bewertet das Fraunhofer IZM im Vorfeld die Ausfallwahrscheinlichkeit der Elemente eines Chiplet-Systems?

Dr. Michael Schiffer: Wir nutzen ein digitales Abbild, um die thermo-mechanischen Analysen mit der Realität abzugleichen. Das heißt mit Hilfe von Simulationen bilden wir den Prozessflow in einem digitalen Zwilling nach, um Fragen zu beantworten wie beispielsweise: Wo treten thermo-mechanische Spannungsspitzen auf, die zum Versagen der Baugruppe führen kann? Wie können wir diese umgehen bzw. verringern? Wie lässt sich der Prozess optimieren, um eine möglichste hohe Ausbeute zu erzielen?

Dr. Andreas Ostmann: Der digitale Zwilling ermöglicht uns vorherzuberechnen, was passieren kann, wenn wir die Kontakte verkleinern oder den Abstand vergrößern, die Schichtdicke variieren und ein neues weicheres Material einsetzen. Wir können die Prozesse in der digitalen Architektur modellieren, ohne sie in der Realität nachzubauen und so Fehler frühzeitig zu erkennen und das Optimum herauszuholen.

Könnten Sie an einem Projektbeispiel erläutern, wie das Fraunhofer IZM zur Entwicklung von Chiplet-Lösungen beiträgt?

Dr. Michael Schiffer: In dem Projekt STXMOD entwickeln wir beispielsweise gemeinsam mit Partnern einen energieeffizienten Stencil-Processor, der zusammen mit und einen High Bandwidth Memory-Speicher (HBM) auf einen Silizium-Interposer für Anwendungen des High Performance Computing eingesetzt wird. Für die Berechnung von beispielsweise Klimamodellen sind Rechenleistungen im Exascale-Bereich erforderlich. Um derart komplexe Berechnungen durchführen zu können, werden spezielle Rechenarchitekturen mit schnellen Speichermodulen, Prozessoren und Hochgeschwindigkeits-Datenbusse benötigt.

Dr. Andreas Ostmann: Wir sind darüber hinaus an weiteren Projekten z.B. an den beiden BMBF-Projekten CeCas und T4T beteiligt. Unsere Kolleg*innen am Fraunhofer IZM-ASSID unterstützen in dem T4T-Projekt »Verteilte Fertigung für neuartige und vertrauenswürdige Elektronik« bei der Fertigung eines 300 mm Wafer-to-Wafer-Demonstrators mit verschlüsseltem Speicherelement sowie eines Interposer-Wafers mit integrierten Chiplets.

Wir haben viel über die Automobilbranche gesprochen. In welchen weiteren Anwendungsfeldern werden Chiplet-Systeme zukünftig zum Einsatz kommen?

Dr. Andreas Ostmann: Die Nachfrage nach leistungsstarken KI-Systemen, nach Anwendungen des maschinellen Lernens (ML), die zunehmende Verbreitung von Geräten für das Internet der Dinge (IoT) und 5G-Technologien treiben die Marktexpansion voran. Marktforschungsinstitute wie zum Beispiel Prudour weisen zudem den Wechsel zur 5G-Konnektivität und das Aufkommen von Edge Computing als weitere Schlüsselfaktoren aus.

Welche langfristigen Zielsetzungen verfolgen Sie in Ihrer jeweiligen Abteilung im Bereich Forschung und Entwicklung?

Dr. Michael Schiffer: An unserem Berliner Standort forcieren wir zum Beispiel Bumpdurchmesser und -pitches im unteren einstelligen µm-Bereich und die Erweiterung der Bumpingmaterialien, um neue Assembly-Technologien zu unterstützen und Kosten zu reduzieren. Wir treiben die Vision der 3D-Hetero-Integration voran und versuchen bei der Umverdrahtung (Anm. der Red: RDL = redistribution layer) so klein wie möglich zu werden, sowohl was die Lines/Spaces, < 4/4 µm, als auch die Vias, < 5 µm, zwischen den Umverdrahtungsebenen anbelangt. In Dresden am Fraunhofer IZM-ASSID planen unsere Kolleg*innen, beim Hybridbonden auf unter 5 µm bis unter 2 µm Pitch zu gehen. Hier steht die High-Performance Applikation im Vordergrund.

Dr. Andreas Ostmann: In meiner Abteilung steht die Fertigungstechnik auf großen Flächen von 510 x 515 mm² bzw. 610 x 456 mm² im Fokus. Bei den organischen Substraten entwickeln wir die Feinstleitertechnologie < 5 µm (Strukturbreite) und < 10 µm (Pitch) weiter. Wir streben Strukturbreiten von 2 µm und kleiner an. Ferner arbeiten wir an Technologien zur Stapelung von 3D-Systemen auf Substratebene.

Vielen Dank für das Gespräch!

Quellen: 1 PRUDOUR 2023, Chiplets Market, Global Industry Analysis, Size, Share, Growth, Trends and Forecast, 2018-2033

Add comment