Dr.-Ing. Charles-Alix Manier erhielt seinen technischen Abschluss in physikalische Messtechnik von der Universität Jean Monnet von Saint-Etienne (FR) und seinen Master-Abschluss in Werkstoffwissenschaften von der Ingenieurschule INSA-Lyon in Frankreich. Er arbeitete im Anschluss an der Bundesanstalt für Materialforschung und -prüfung in Berlin in der Tribologie und promovierte 2010 an der Technischen Universität Berlin.

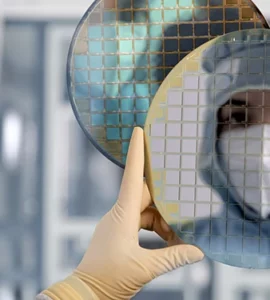

Seit 2010 ist er am Fraunhofer IZM als Forscher in der Gruppe Fine Pitch Assembly and Interconnects (FPAI) tätig und arbeitet an Flip-Chip- und Die-Bonding-Technologien (einschließlich Reflow-Löten, Thermokompression, Transient Liquid Phase Bonding) in verschiedenen Anwendungsbereichen (u.a. MEMS, Leistungselektronik, Medizin). Er leistet hauptsächlich Beiträge im Bereich Chip-to-Chip/Substrat, Chip-to-Wafer-Bonden, vakuumdichtes hermetisches Versiegeln von MEMS-Komponenten und Integration von Halbleiterchips mit breiter Bandlücke für Hochleistungsanwendungen, sowohl im Rahmen europäischer (öffentlich finanzierter) Projekte als auch in Partnerschaftsprojekten.

3D-Integration 5G 6G Antennen Autonomes Fahren Batterietechnologie Bio-Elektronik Chiplets Digitaler Zwilling Drahtlose Kommunikation Electronic Packaging Elektronische Textilien Embedding Energielabel Flip-Chip Funksensoren Grey-Box-Modellierung Halbleiter Hardwaresicherheit Hetero-Integration Hochleistungscomputer IKT Implantate Industrie 4.0 Internet der Dinge Kreislaufwirtschaft Künstliche Intelligenz Laserschweißen Lebenszyklusanalysen für Elektronik Leistungselektronik Maschinelles Lernen Medizintechnik Nachhaltige Elektronik Photonisch Integrierte Schaltungen Quantum Technologien Radar Sensorik Wafer-Level-Capping Wafer-Level-Packaging Wissenschaftskommunikation Zirkuläres Design Zuverlässigkeit Öko-Design elektronischer Produkte