RealIZM-Blog-Serie »Hardwaresicherheit« – Teil 3

Die sichere Versorgung mit elektronischen Bauteilen ist für den Industriestandort Deutschland von strategischer Bedeutung. Angesichts der zunehmenden Verlagerung der Fertigung von integrierten Schaltkreisen (IC) in außereuropäische Regionen wächst jedoch die Gefahr, dass Schad- und Spionagefunktionen in die gelieferten elektronischen Bauteile eingebracht werden.

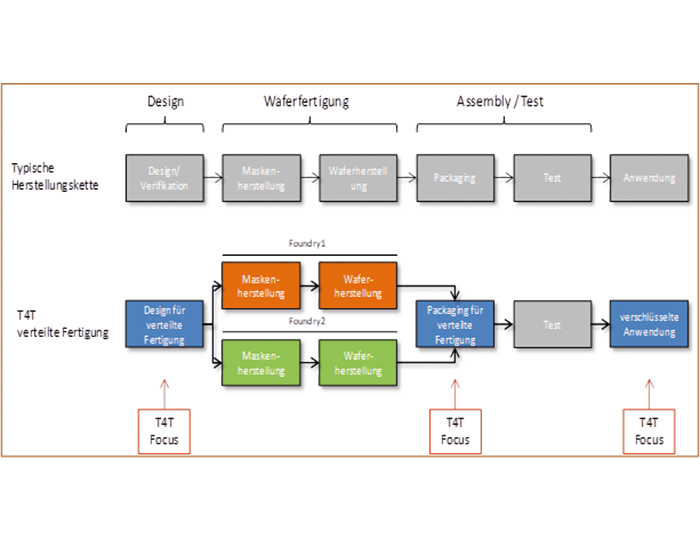

Um dieses Risiko zu minimieren, arbeiten Fraunhofer-Institute und deutsche Industrieunternehmen im Rahmen des Verbundprojekts T4T »Tech-for-Trust: Verteilte Fertigung für neuartige und vertrauenswürdige Elektronik« an einem innovativen Split-Manufacturing-Ansatz für die Halbleiterfertigung. Durch die sichere Montage und Verschlüsselung der Elektronik-Systeme in Deutschland sollen Spionage und Diebstahl geistigen Eigentums im Schaltungsdesign verhindert werden.

Die heterogene Integration – das Zusammenfügen von Chip-Komponenten aus unterschiedlichen Technologien und Fertigungsstätten – ist sowohl aus technischer als auch aus wirtschaftlicher Sicht attraktiv. Sie erhöht die Flexibilität in der Chip-Herstellung und senkt die Kosten. Zugleich bestehen noch viele offene Forschungsfragen unter anderem hinsichtlich der Entwicklung multifunktionaler Substrate, der Erhöhung der Vertrauenswürdigkeit und der Hardwaresicherheit des elektronischen Gesamtsystems.

Ein Ansatz zur Steigerung der Vertrauenswürdigkeit von elektronischen Bauelementen besteht darin, diese unabhängig voneinander an verschiedenen Standorten – auch außerhalb Europas – zu fertigen und anschließend in Deutschland mithilfe von Aufbau- und Verbindungstechniken (AVT), wie etwa dem Die-to-Wafer (D2W)- oder Wafer-to-Wafer (W2W)-Bonden, zu einem vertrauenswürdigen Gesamtsystem zusammenzuführen. Voraussetzung hierfür ist, das Fertigungsdesign so zu definieren, dass trotz der zahlreichen beteiligten Akteure eine sichere Lieferkette bei der Halbleiterfertigung gewährleistet wird.

Der Vorteil des Split Manufacturing liegt darin, dass die beteiligten Hersteller und Lieferanten der elektronischen Komponenten keine Rückschlüsse auf das Gesamtsystem ziehen können. Ein Nachbau ist somit ausgeschlossen. Nur der Verantwortliche für das Design verfügt über alle Informationen zum Gesamtsystem. Zur zusätzlichen Absicherung kann während der Herstellung ein kryptografischer Schlüssel integriert werden.

T4T verteilte Fertigung und Fokus des Projektes | © Fraunhofer IZM-ASSID, Thomas Werner

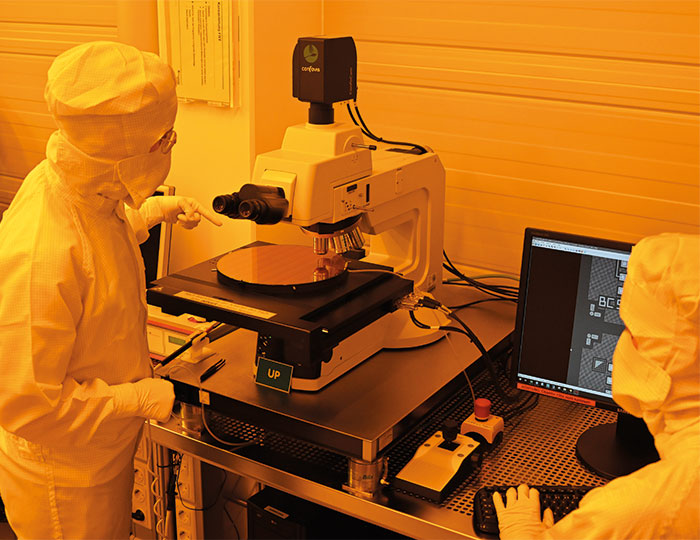

Das Fraunhofer IZM-ASSID und seine Projektpartner bearbeiten im T4T-Projekt verschiedene Arbeitspakete, z.B. zu Entwurfsmethodik für Split-Manufacturing, Komponenten der Aufbau- und Verbindungstechnologien (AVT) und Demonstratoren. Die meisten technologischen Demonstratoren entstehen auf der Basis von der 300-mm Fertigung. Der Fokus für das Fraunhofer IZM-ASSID im AVT liegt auf der stabilen Prozessintegration sehr kleiner Kontakte mittels unterschiedlicher Verbindungstechnologien: Hybridbonding mit Kupfer-/Siliziumoxid-Kontakten, Nanowire-Verbindungen und Mikrobumps.

Ziel ist es, bei allen Technologien die 5 µm kleinen Kontakte auf einem 10 µm Pitch zu realisieren – von der Designphase bis zum D2W-Bonden. Auch das Thema verschiedener Chiplet-Größen wird in diesem Projekt aktiv angegangen. All diese Technologien sind im Bereich High-Performance-Computing notwendig, das durch sehr hohe Kontaktdichten gekennzeichnet ist.

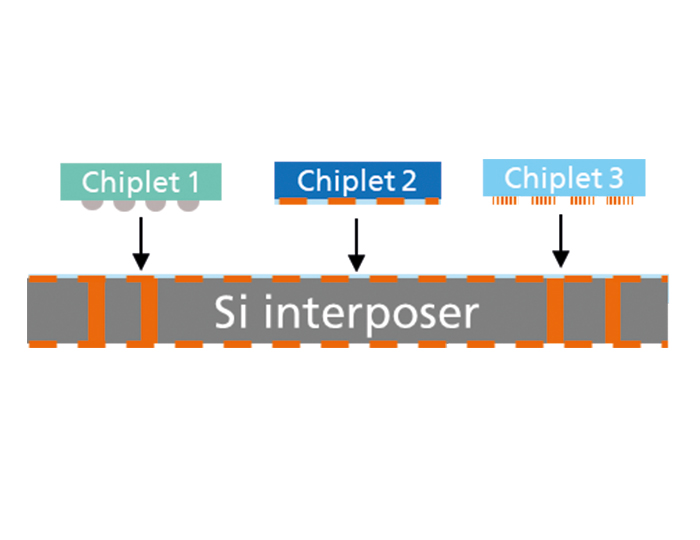

Schematische Darstellung eines Si-Interposers mit Mikrobump, Hybridbond und Nanowire-Chiplets | © Fraunhofer IZM-ASSID, Prof. Dr.-Ing. Juliana Panchenko

Entwicklung innovativer Demonstratoren basierend auf dem Hybridbonden

Im Projekt T4T werden mehrere Demonstratoren erarbeitet. Das Fraunhofer IZM-ASSID entwickelt einerseits einen Technologiedemonstrator zur Chiplet-Integration auf 300 mm Si-Interposern. Andererseits beteiligt sich das Institut an einem Demonstrator, der federführend vom Fraunhofer IPMS entwickelt wird. Dieser Demonstrator besteht aus einem W2W-Hybrid-Bond-Stack aus zwei Wafern mit verschlüsseltem Speicher, für High-End-Anwendungen mit höchsten Anforderungen an Leistung, Zuverlässigkeit und Effizienz.

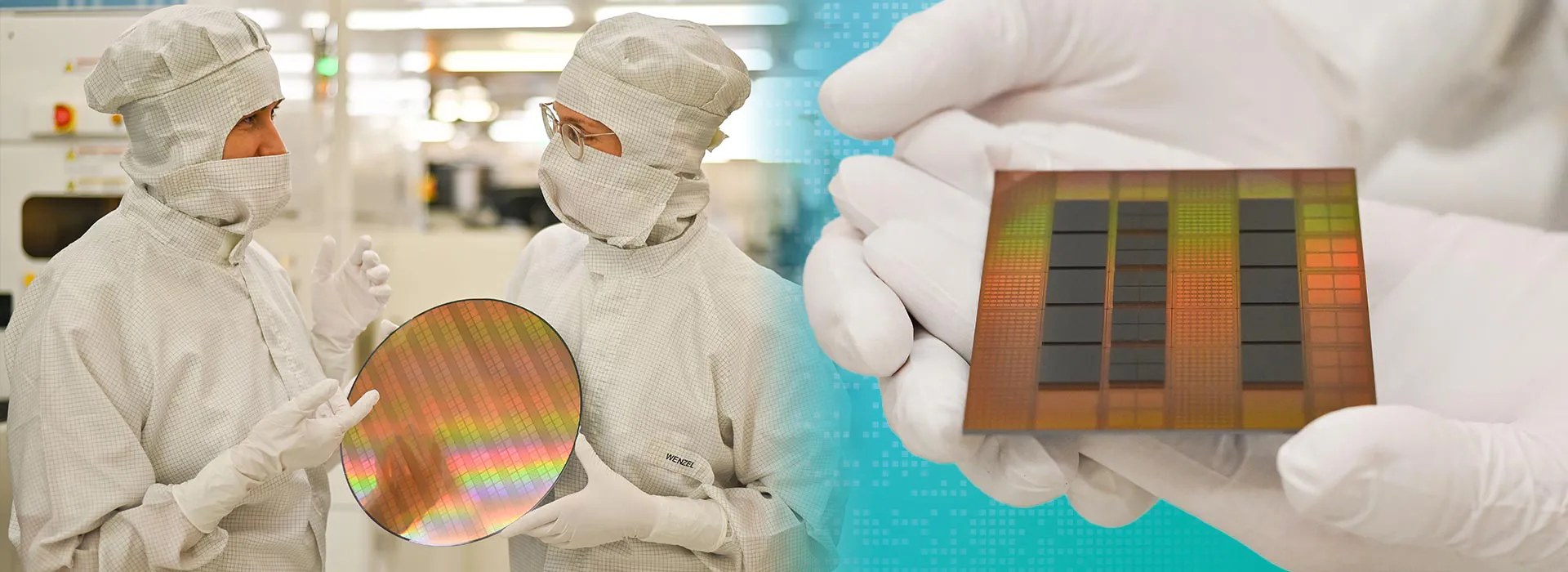

Links: Demonstrator: Montierte Chiplets mit ultra-feinen Kupfer-Hybridbondkontakten auf einem Pitch von 10 µm | © Fraunhofer IZM-ASSID, Silvia Wolf

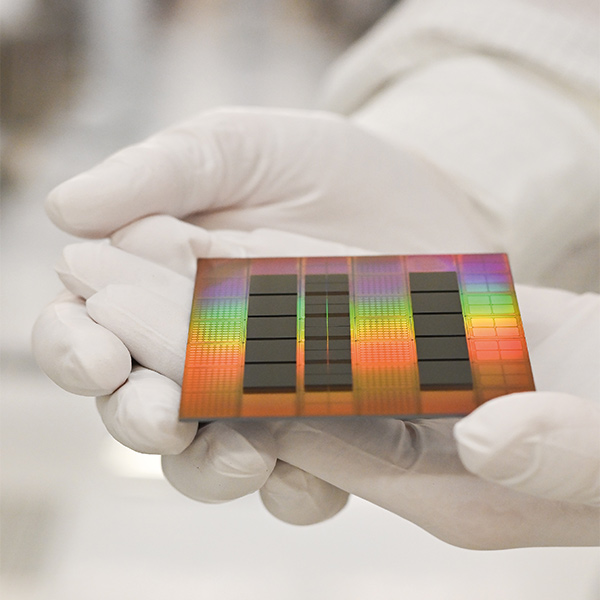

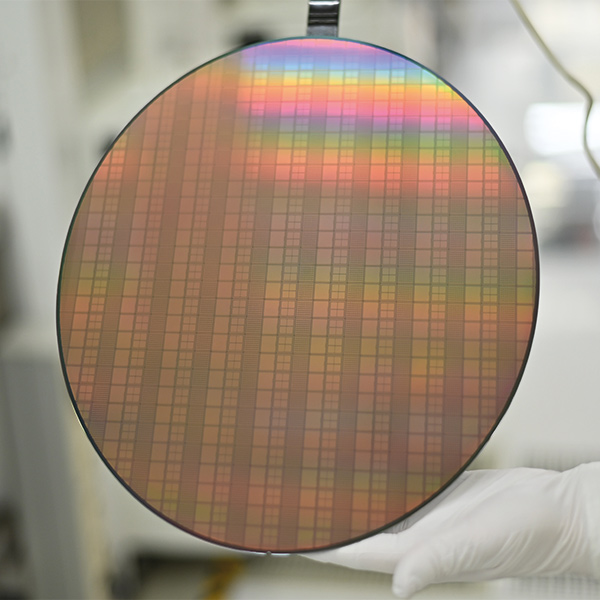

Rechts: Demonstrator: 300 mm Si-Wafer mit hochdichten Kupfer-Verbindungen für die Chiplet-Integration im Rahmen des Projekts »T4T« | © Fraunhofer IZM-ASSID, Silvia Wolf

Der Chiplet-Demostrator soll die Möglichkeit einer Kombination aus mindestens zwei Verbindungstechnologien auf einem Si-Interposer demonstrieren. Es ist zu erwarten, dass Chiplets in Zukunft nicht nur aus einer einzigen Foundry stammen und ein einheitliches Kontakt-Finish aufweisen werden. Stattdessen werden sie verschiedene Oberflächen haben. Sowohl Chiplets mit Lot- als auch mit DBI- Oberfläche (Direct Bond Interconnect) müssen auf Interposern miteinander verbunden und verarbeitet werden.

Außerdem werden die Chiplets in Zukunft unterschiedliche Größen haben (wenige mm bis cm). Mit dem Chiplet-Demonstrator sollen diese Themen angegangen werden. Geplant ist es, die Chiplets mit unterschiedlicher Größe und je unterschiedlicher Oberfläche (Hybridbond Chiplet vs. Nanowire Chiplet, Hybridbond Chiplet vs. Mikrobump Chiplet) auf einem Si-Interposer zu bonden und zu charakterisieren. An dieser Stelle erweitert Fraunhofer IZM ASSID die Kooperation mit dem technologischen Partner NanoWired, welcher die Prozessierung von Nanowire-Chiplets unterstützt.

Der zweite Demonstrator, W2W-Hybrid-Bond-Stack mit verschlüsseltem Speicher, veranschaulicht den Split-Manufacturing-Ansatz, bei welchem die einzelnen Wafer in verschiedenen Fabriken vorbereitet werden. In diesem Fall übernehmen die Prozessierung das Fraunhofer IPMS-CNT und das Fraunhofer IZM-ASSID. Die kryptografische Verschlüsselung des Wafers verantworten das Fraunhofer IPMS-CNT und der Projektpartner SIJEDA.

Links: Hybridbond Interconnects mit 10 µm Pitch | © Fraunhofer IZM-ASSID, Prof. Dr.-Ing. Juliana Panchenko

Rechts: Demonstrator: 300 mm Si-Wafer mit hochdichten Kupfer-Verbindungen für die Chiplet-Integration im Rahmen des Projekts »T4T« | © Fraunhofer IZM-ASSID, Silvia Wolf

Herausforderungen und Lösungen für Bond-Prozesse im Split-Manufacturing

Voraussetzung für die erfolgreiche Umsetzung des Split-Manufacturing-Ansatzes ist eine sehr gute Abstimmung zwischen den Beteiligten. Für das Team des Fraunhofer IZM-ASSID ist es entscheidend zu wissen, wie die Komponenten der verschiedenen Zulieferer aussehen, die mit den verfügbaren AVT-Methoden gebondet werden sollen. Normalerweise wird ein Si-Interposer für High-Performance Packaging-Anwendungen mit einer DBI (oder Hybridbond-Oberfläche) vorbereitet. Diese Oberfläche ist entscheidend, wenn Chiplets mit DBI-Kontakten darauf platziert werden sollen.

Sobald ein weiteres elektronische Bauteil hinzukommt, muss geprüft werden, ob und wie die Zuverlässigkeit auch langfristig gewährleistet werden kann. Gegebenenfalls sind die Chiplets mit den DBI-Kontakten zusätzlich aufzubereiten, z.B. durch Abdünnen, Integration in die Waferlinie und Aufbringen spezieller Pads, um das Bonden anderer Chiplets, z.B. mit Lot, zu ermöglichen. Die große Herausforderung besteht darin, die genaue Abfolge der Bonding-Prozesse und die erforderlichen Technologien sowie Prozessschritte festzulegen.

Bei der Integration von Chiplets mit zahlreichen Kontaktstellen müssen zunächst die technologischen Voraussetzungen geschaffen werden, um diese in einem Bondtool zu kombinieren. Dabei spielen nicht nur die Größe der Chiplets eine Rolle, sondern auch, wie die Verbindungsstellen prozessiert werden und in welcher Reihenfolge die Chiplets auf den Interposer gebondet werden können. Zudem muss die Oberflächengestaltung des Interposers technologisch durchdacht sein, um die unterschiedlichen Chiplets kombinieren zu können. Die Designoptimierung der Interposer-Oberfläche ist besonders wichtig, wenn Chiplets verschiedener Größen genutzt werden.

Beim Bonden muss eine Prozessabfolge für die Platzierung größerer und kleinerer Chiplets mit verschiedenen speziellen Pick-Up Tools evaluiert werden. Besonders bei sehr großen Chiplets mit einer Kantenlänge über 20 mm mit sehr kleinen Verbindungsstellen ist eine homogene Chipletoberfläche und eine extrem planparallele Ausrichtung der zu bondenden Oberflächen entscheidend. Schon kleinste Abweichungen können zu erheblichen Yield-Verlusten führen.

Im Projekt T4T wird aufgezeigt, dass diese Chiplet-Bondtechnologie für sehr kleine Kontakte am Standort Deutschland möglich ist. Das Fraunhofer IZM-ASSID arbeitet daran, robuste und stabile Prozesse für kleine Kontakte (basierend auf dem Hybridbonden, Nanowire und Mikrobump) für das D2W-Bondverfahren auf 300 mm Wafern zu entwickeln. Das Projekt T4T ermöglicht die Entwicklung der Laser-Direkt-Imaging (LDI) Strukturierungsmethode, mit der winzige Strukturen bis zu 0,75 µm ohne zusätzliche Masken hergestellt werden können.

Aktuell existieren weder Standards für die Herstellung von hochintegrierten Aufbauten mit Chiplets und W2W-Abläufen noch Designregeln oder Assembly Design Kits (ADKs). Gemeinsam mit dem Fraunhofer IIS-EAS erarbeitet das Fraunhofer IZM-ASSID daher auch Prozessabläufe für die Designphase einer verteilten Fertigung und überprüft das Design auf die technologische Machbarkeit. Ferner hat das Projektkonsortium eine Roadmap zur »Konzeptionierung eines arbeitsteiligen Ökosystems für das Advanced Packaging in der Mikroelektronik« insbesondere für Standort Deutschland aufgestellt.

Ausblick: Fraunhofers Weg zur Spitzenforschung in der Chiplet-Integration

Hybridbonden ist die Enabler Technologie, die das zuverlässige Stapeln von Silizium-Chiplets mit sehr hoher Kontaktdichte (Pitch unter 15 µm, Kontaktdurchmesser unter 10 µm) ermöglicht. Dies erlaubt den Aufbau von Systemen mit hoher Leistungsfähigkeit, hohen Datenraten, langer Lebensdauer und geringer Latenz. Fraunhofer zielt auf den Einsatz dieser Technologie für 2,5D/3D Aufbauten mit sehr kleinen Kontakten. Für größere Kontakte können sowohl Mikrobump- als auch neue Nanowire-Technologien erfolgreich eingesetzt werden, die Vorteile bei Prozesskosten und Prozesstemperaturen bieten.

Die gewonnen Erkenntnisse aus dem Projekt T4T werden in die neue Fraunhofer-Initiative »Chiplet Center of Excellence (CCoE)« einfließen.

Veröffentlichungen:

- Influence of Heat Treatment on the Quality of Die-to-Wafer Hybrid Bond Interconnects

- Investigation of Side Wall Loss for Development of 6 µm Micro Bumps for 3D/2.5D Integration

- Fine-Pitch Copper Nanowire Interconnects for 2.5/3D System Integration

- Cu nanowire fine-pitch joints for next gen heterogeneous chiplet integration

- Microstructure Development of Cu/SiO2 Hybrid Bond Interconnects After Reliability Tests

T4T »Tech-for-Trust: Verteilte Fertigung für neuartige und vertrauenswürdige Elektronik«

Das Projekt T4T »Tech-for-Trust: Verteilte Fertigung für neuartige und vertrauenswürdige Elektronik« ist ein vom BMBF gefördertes Verbundprojekt zur Ermöglichung einer sicheren Lieferkette durch verteilte Fertigung (Split-Manufacturing) am Standort Deutschland.

Projektträger:

VDI/VDE Innovation + Technik GmbH

Fördergeber:

BMBF

Verbundkoordinationsteam:

Robert Bosch GmbH

Fraunhofer IZM-ASSID

Projektpartner:

ams-OSRAM International GmbH

AUDI AG

DISCO HI-TEC GmbH

NanoWired GmbH

X-FAB Dresden GmbH & Co. KG

X-FAB MEMS GmbH

Fraunhofer IIS-EAS

Fraunhofer IPMS

Fraunhofer IZM-ASSID

Leibniz-Institut für innovative Mikroelektronik

Technische Universität Dresden

SIJEDA GbR (assoziierter Partner)

SÜSS MicroTec AG (assoziierter Partner)

Laufzeit & Förderkennzeichen:

04/2022 – 03/2025 | 16ME0481

Mehr Informationen zu Fraunhofer IZM Lösungen für die Herausforderungen in der Hardwaresicherheit.

Add comment