Wussten Sie, dass die Miniaturisierung von Mikrochips und die Entwicklung smarter Geräte maßgeblich auf einer nahezu unsichtbaren Verbindung basiert: den Substraten? Diese hochaufgelösten und fein strukturierten Substrate sind der Schlüssel zur modernen Elektronik.

Ruben Kahle, wissenschaftlicher Mitarbeiter in der Gruppe »Embedding & Substrate Technologies« am Fraunhofer IZM, lud das RealIZM-Blogteam zu einem exklusiven Videorundgang in den Berliner Reinraum ein. Wir haben die Kamera eingepackt, unsere Bürokleidung mit Schutzanzügen getauscht und die Welt des Reinraums betreten.

Folgen Sie uns! Erhalten auch Sie einen faszinierenden Einblick in die Welt der HDI-Substrate und entdecken Sie deren vielseitige Einsatzmöglichkeiten.

Substrate sind das Bindeglied zwischen den Strukturen der Leiterplatte und den Ein- und Ausgängen von Hochleistungs-Mikrochips. Sie bilden die Brücke zwischen der Mikrowelt der Leiterplatten und der Nanowelt der Halbleiterindustrie. Ähnlich wie das Fundament eines Hauses fungieren Substrate als Basisschicht einer Leiterplatte und sind eine zentrale Voraussetzung für die Datenverarbeitung auf Mikrochips.

Mit der fortschreitenden Miniaturisierung elektronischer Bauteile und der stetig steigenden Nachfrage nach Netzwerken der Künstlichen Intelligenz (KI) wird auch die Entwicklung von Leiterplatten und Chips immer komplexer. Elektronische Produkte und Anwendungen mit höherwertigen technischen Funktionen gehen mit Anforderungen wie z.B. Energieeffizienz, Kostensenkung durch Material- und Platzersparnis sowie einer Ressourcenschonung einher.

Die Abkürzung HDI steht für High Density Interconnect(ion). Die Verwendung von HDI-Substraten erfordert Semi-Additivverfahren, gestapelte µVias und Dielektrika, die partikelgefüllt oder ungefüllt sind.

Als Pure-Play-Foundry bietet das Fraunhofer IZM im Bereich der Forschung und Entwicklung umfassende Lösungen aus einer Hand – von der Layoutgestaltung über die Materialauswahl bis zur Produktion. »Mit dem uns zur Verfügung stehenden Technologie-Portfolio können wir Substrate mit Glaskernen und organische IC-Substrate fertigen und die Umverdrahtung auf gemoldeten Panels (FOPLP) erzeugen«, erläutert Ruben Kahle die Möglichkeiten am Fraunhofer IZM.

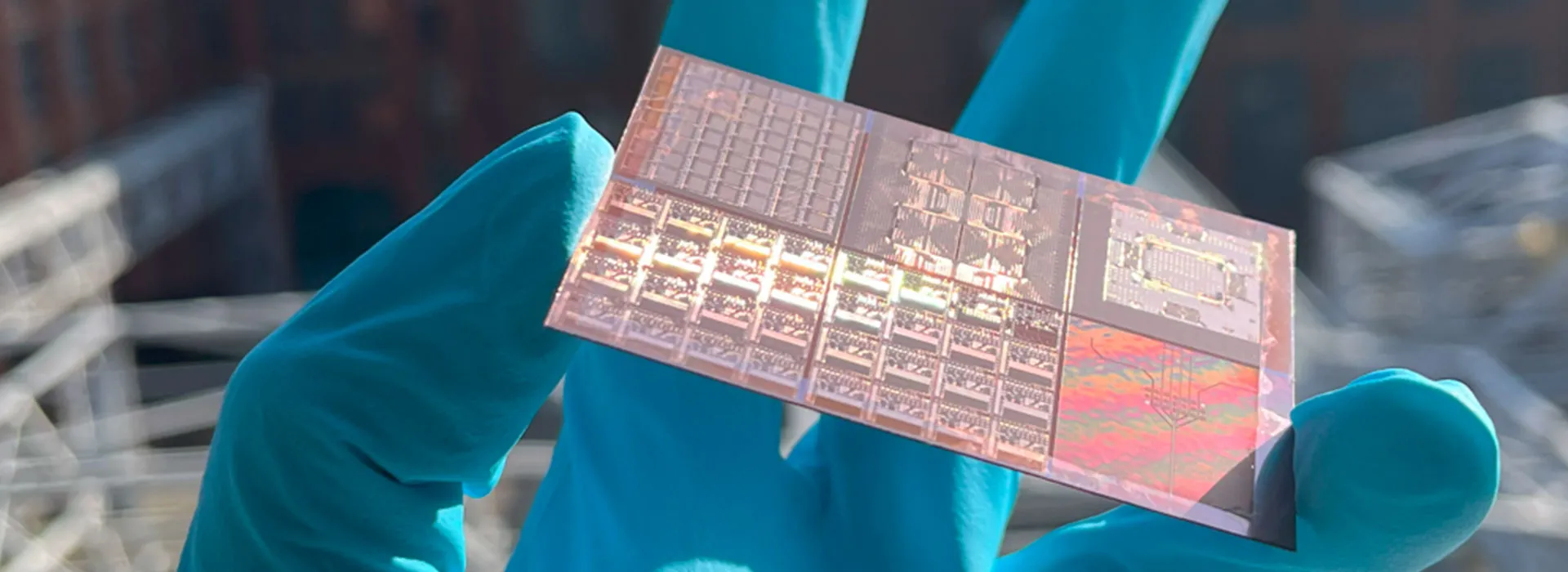

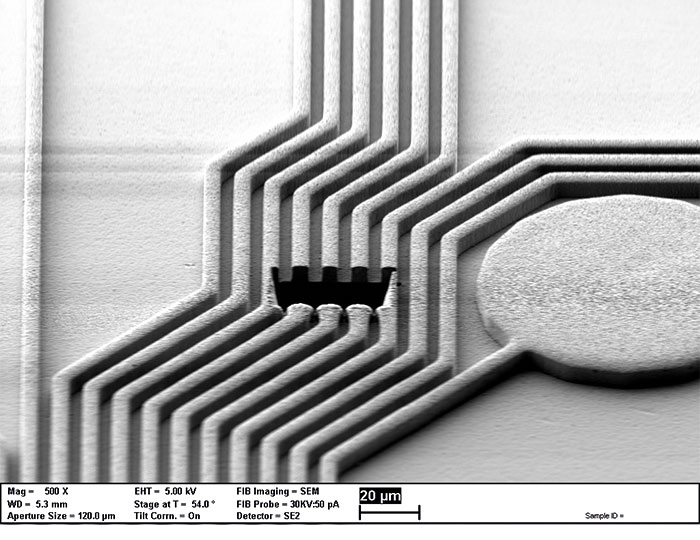

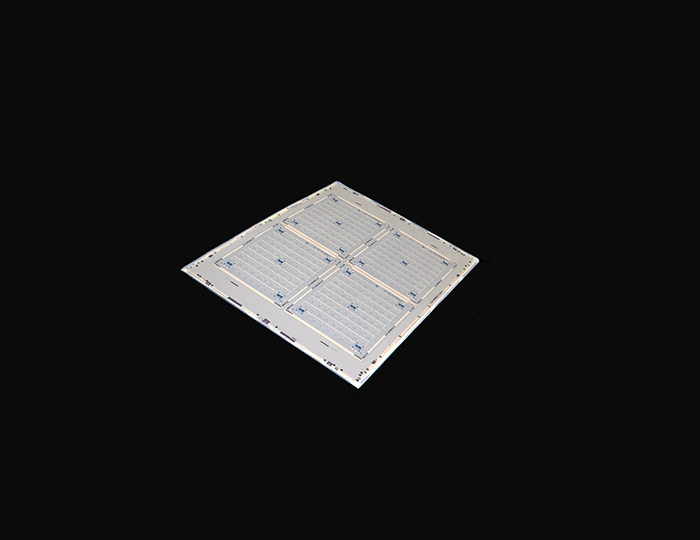

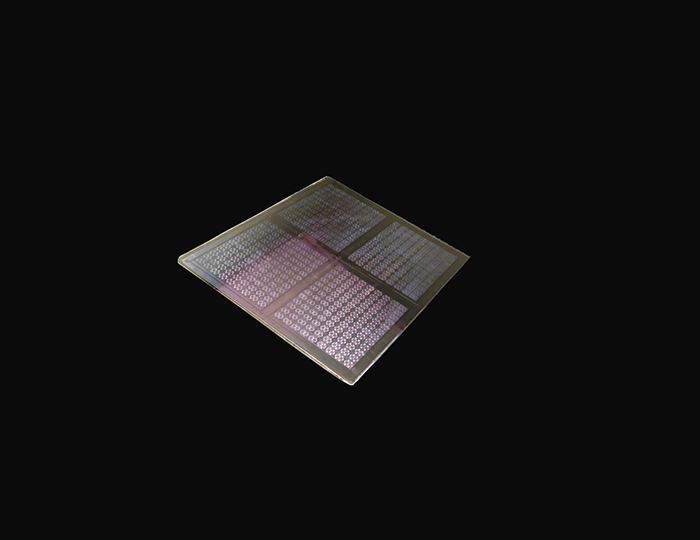

Links: Glaskernsubstrat (GCS) mit hochdichter Testschicht aus strukturiertem Kupfer auf 2 mm Glas für Demonstrationszwecke

Mitte & Rechts: Montage der Dies in den Hohlräumen auf der vollen Substratgröße von 510 mm x 515 mm vor dem Einbetten

© Fraunhofer IZM

Die Entwicklung von HDI-Substraten wird vorrangig durch die Wünsche der Auftraggeber*innen und die Fortschritte in der Wafer-Technologie angetrieben. »Das Design von HDI-Substraten und der Produktionsprozess als Teil unseres Arbeitsgebietes sind einem ständigen Wandel unterlegen«, erklärt Kahle.

»Das Substrat-Design orientiert sich am Chip-Design. Die Anzahl der Lagen und die Anzahl der notwendigen Kontaktstellen, Leiterbahnen und Verbindungen in und vom Substrat weg nimmt zu. Das heißt, wir sind daher auf Softwarelösungen angewiesen, die ein System oder Package ganzheitlich betrachten können.«

Hinzu kommt, dass die Produktionsprozesse der konventionellen Leiterplattentechnik an ihre physikalischen Grenzen stoßen. Für die Erzeugung feiner Strukturen in Kupfer lassen sich die klassischen Prozesse nur bis zu einem gewissen Maß weiter miniaturisieren. Die Prozessketten für HDI-Substrate und deren Folgegenerationen sind daher an die Halbleitertechnologie angelehnt z.B. PVD-Sputtern, Damaszentechnik oder fotostrukturierbare Dielektrika. Diese Prozesse basieren jedoch auf einem kleinen runden Format (Wafer mit Durchmessern von 200 mm oder 300 mm).

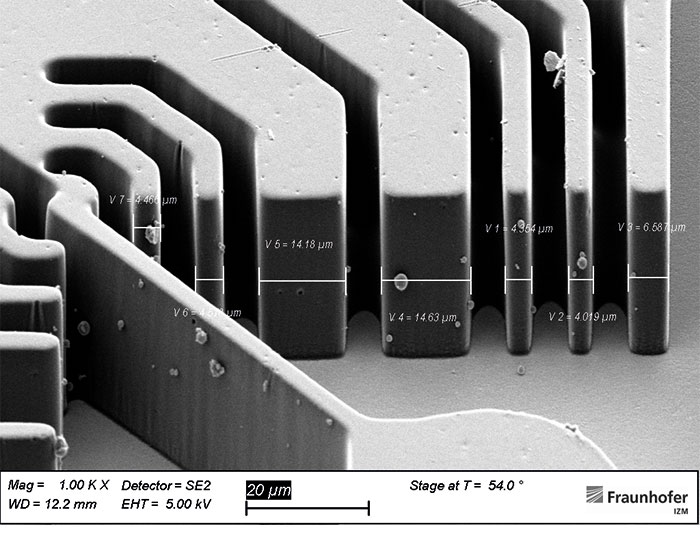

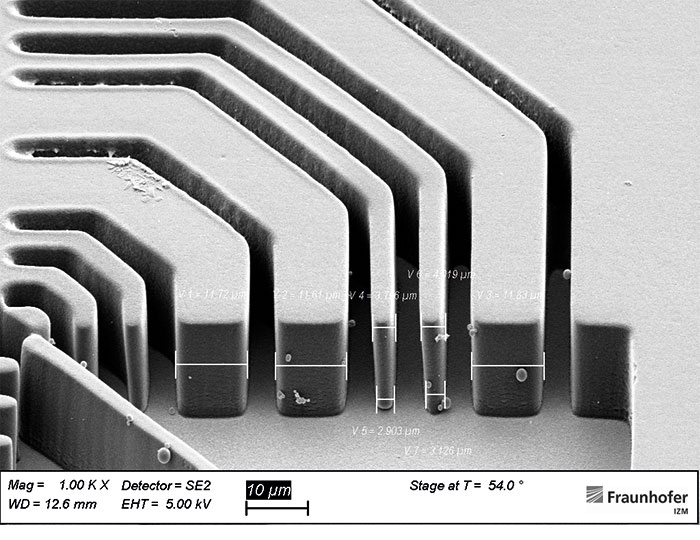

Link: Redistribution Layer (RDL) Leiterbahn 5 µm L/S mit einer Kontaktfläche von 50 µm Durchmesser

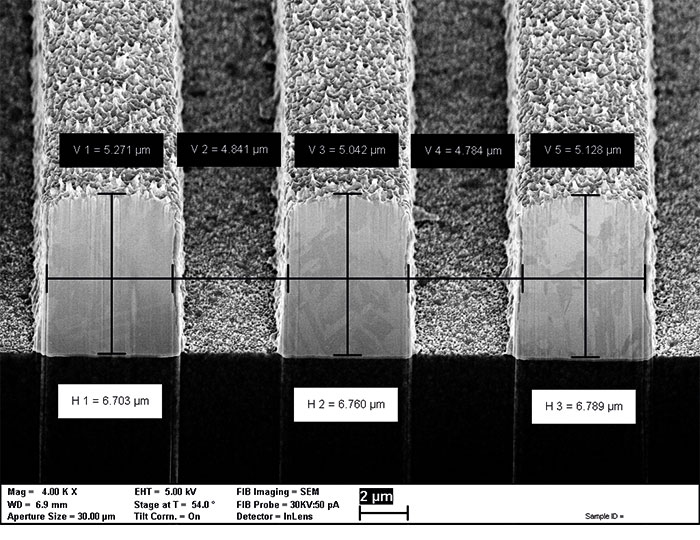

Mitte: FIB-Schnitt (Focused-Ion-Beam) durch den Bereich einer Umverdrahtungsschicht (RDL) 5 µm L/S

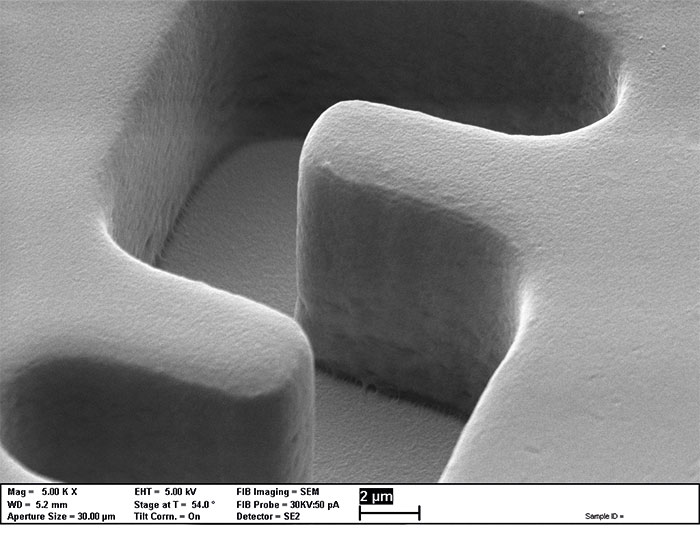

Rechts: Rasterelektronenmikroskop-Aufnahme (REM) eines 5 µm L/S-Fotolacks nach der Entwicklung, Filmdicke 7 µm

© Fraunhofer IZM

REM-Aufnahme eines 5 µm L/S-Fotolacks nach der Entwicklung, Filmdicke 25 µm © Fraunhofer IZM

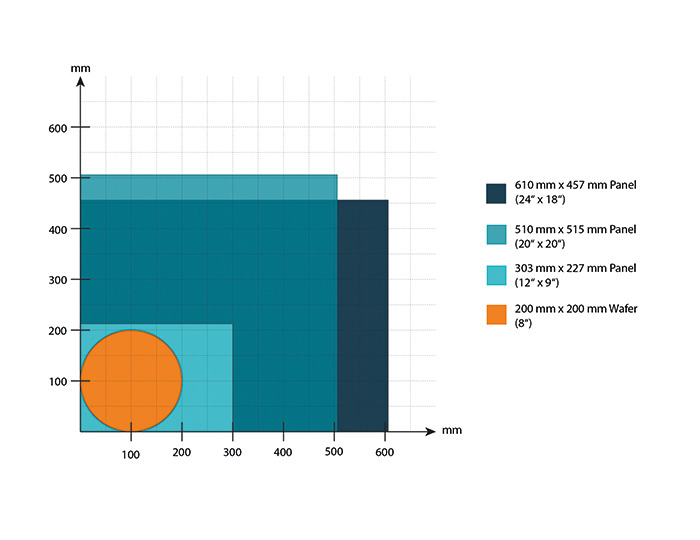

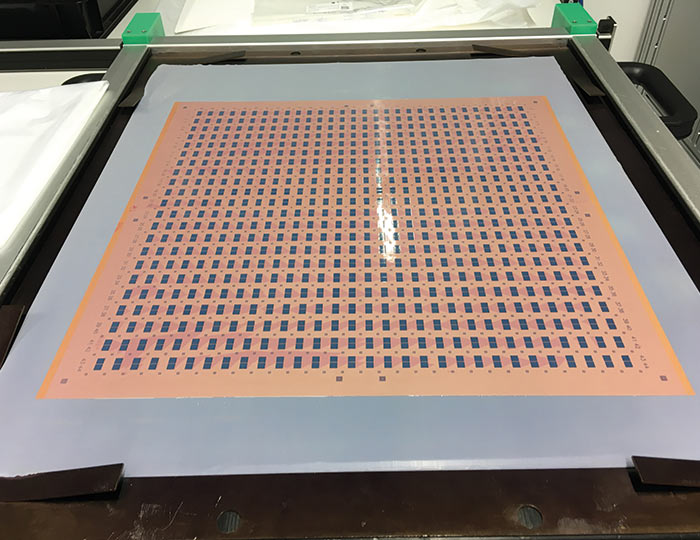

»Wir müssen daher jeden einzelnen Schritt in der Fertigungskette skalieren und auf ein großes, rechteckiges Format (Panel) anpassen«, beschreibt Kahle die Herausforderungen bei der Umsetzung. Am Fraunhofer IZM sind die Maschinen und das Material im Reinraum auf die Fertigung von HDI-Substraten abgestimmt, um die Formate 510 mm x 515 mm, 610 mm x 457 mm (24“ x 18“) und dessen Viertelgröße 303 mm x 227 mm (12“ x 9“) realisieren zu können.

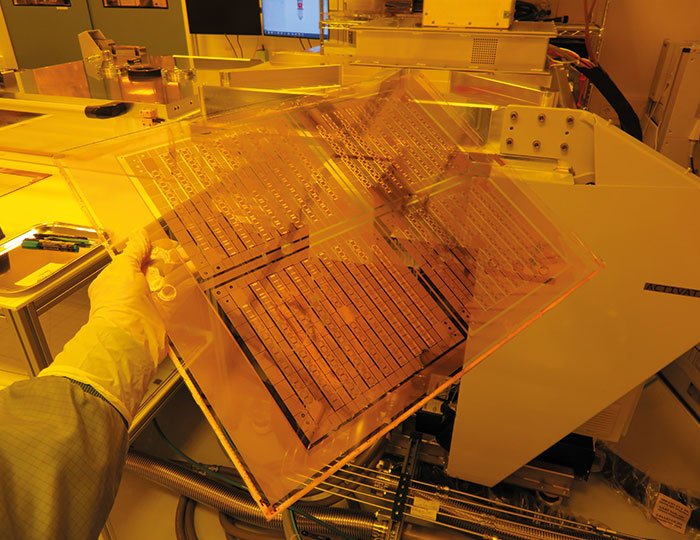

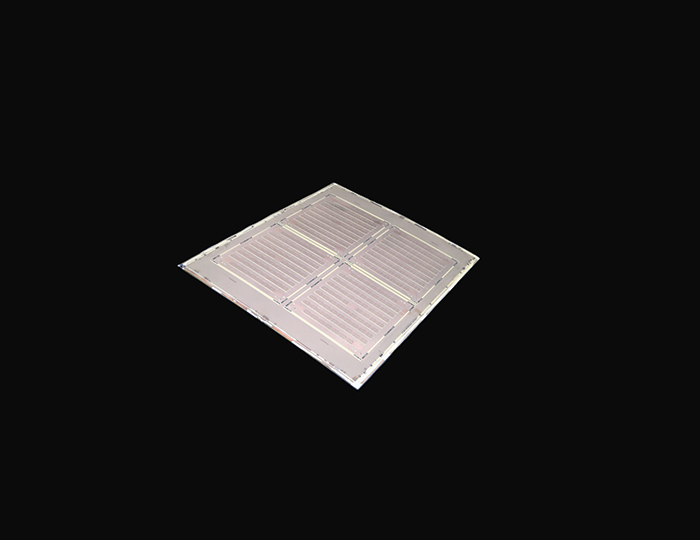

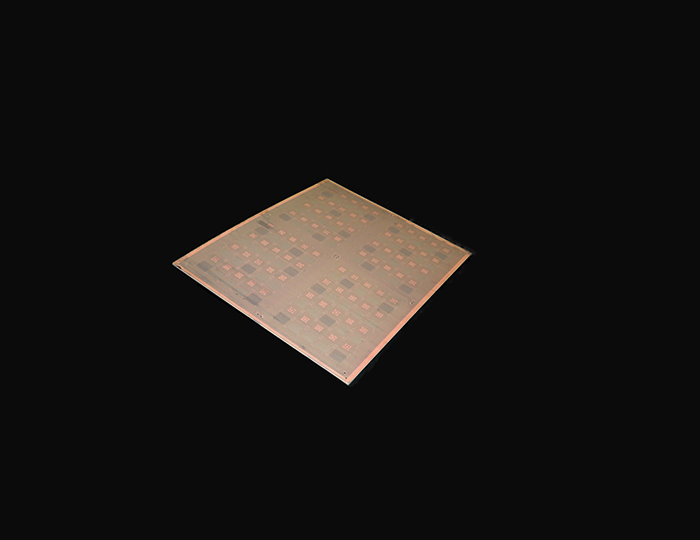

Links: 610 x 457 mm Substrat mit eingebetteten Chips in Zusammenarbeit mit Projektpartnern im Projekt CHARM

Rechts: 610 x 457 mm Substrat mit mehrlagiger Verdrahtung

© Fraunhofer IZM | Francis Viebeck

Links: 610 x 457 mm Substrat mit eingebetteten Chips nach der ersten Umverdrahtungslage

Rechts: 610 x 457 mm Substrat mit strukturiertem Resist nach der Lithographie zu Qualitätsprüfung

© Fraunhofer IZM | Francis Viebeck

Grafik: Panel-Größe HDI-Substrate | © Fraunhofer IZM

»Je nach Spezifikation unserer Kunden fertigen wir Prototypen und Kleinserien mit den HDI-Substraten ab 5 µm L/S aufwärts an. Zu Forschungs- und Entwicklungszwecken sind wir in der Lage, auch unter 5 µm L/S bis derzeit minimal 2 µm L/S zu gehen. Wir befinden uns dabei in einem experimentellen Stadium.«

Die Verwendung von HDI-Substraten bringt zahlreiche Vorteile mit sich, die sie zu einer bevorzugten Wahl in der modernen Elektronik machen. Substrate bieten nicht nur eine erhöhte Packungsdichte und verbesserte elektrische Leistung, sondern ermöglichen auch eine flexible Gestaltung komplexer Schaltungen.

- Kompakte Bauweise: Höhere Packungsdichte durch feinere Leiterbahnen, deutlich kleinere Vias und mehr Lagen. Ideal für tragbare Geräte und Anwendungen mit begrenztem Bauraum.

- Verbesserte elektrische Leistung: Kürzere Signalwege reduzieren Signalverluste und erhöhen die Signalgeschwindigkeit.

- Erhöhte Designflexibilität: Möglichkeit, komplexe Schaltungen effizient zu integrieren, da man Vias stapeln kann (Any-Layer-Technik).

- Zuverlässigkeit: Weniger Lötstellen und Verbindungen verringern potenzielle Fehlerquellen.

- Thermisches Management: Bessere Wärmeableitung durch dünnere Materialien und optimierte Layer-Anordnung.

- Einsatz moderner Bauteile: Ermöglicht die Verwendung kleinerer, leistungsstärkerer ICs und fortschrittlicher Chips (z. B. BGA, CSP oder bare dies).

- Anpassung an hohe Frequenzen: Ideal geeignet für Anwendungen in der Telekommunikation (5G), in IoT-Geräten und Hochgeschwindigkeitskommunikation.

Leiterplatten mit hoher Verbindungsdichte kommen unter anderem in Consumer Electronics wie z.B. Smartphones, Digitalkameras, Laptops und Tablets zum Einsatz. So profitieren USB-C- und Thunderbolt-Anschlüsse von der Hochgeschwindigkeits-Datenübertragung von HDI-Leiterplatten.

Moderne Fahrassistenzsysteme basieren auf Radar- und Kamerasystemen, in denen ebenfalls HDI-Leiterplatten verwendet werden. Dank ihrer sehr guten Signalintegrität und Langlebigkeit eignen sich HDI-Leiterplatten zudem für Anwendungen in der Luft- und Raumfahrt und Verteidigung z.B. in Radarsystemen, GPS und anderen Navigationssystemen.

Auch die Medizintechnik bietet vielfältige Einsatzmöglichkeiten z.B. bei der Realisierung von miniaturisierten Ultraschallgeräten oder tragbaren Monitoren zur Überwachung der Herzfrequenz.

Projektbeispiel CHARM: Elektroniksysteme für extrem robuste IoT- und KI-Anwendungen

Im Rahmen des CHARM-Projekts der ECSEL-Verbundinitiative hat das Fraunhofer IZM gemeinsam mit seinen Projektpartnern Lösungen für das industrielle Internet der Dinge (IoT) entwickelt, die in harschen industriellen Umgebungen zuverlässig arbeiten. In diesem Projekt wurden Lösungen für sechs Anwendungsfälle im Bereich Zustandsüberwachung, vorrauschauender Wartung und Echtzeit-Qualitätssicherung erarbeitet, einschließlich IoT-Anwendungen im Montansektor. Der Schwerpunkt des Teilprojektes lag auf der Entwicklung von Radarsensoren, die das autonome Fahren von Abbaumaschinen im »Digitalen Bergbau« ermöglichen sollen.

Das Fraunhofer IZM hat seine Expertise in der Prozessentwicklung für die zuverlässige Integration von Siliziumkomponenten in Substrate und derer Kontaktierung in das Projekt eingebracht. In Zusammenarbeit mit AT&S wurde ein Embedded Computer Module entwickelt. Zudem fanden Versuche zur Herstellung der Umverdrahtung mikroelektronischer Komponenten (High Density Wiring) in Aufbausubstraten unter Anwendung fortschrittlicher Strukturierungsverfahren statt.

Einbetten von High-IO-Nacktchips in IC-Substrate

Projekt CHARM ECSEL JU

Beitrag des Fraunhofer IZM:

Adaptive Panel Layout (APL), basierend auf präziser AOI-Messung und für Multicore optimierter Software zur Umverdrahtung jedes Panels

SAP-basierter Aufbau, RDL mit 5 µm L/S auf ABF GXT62

Spezifikationen:

Die: 26 mm x 18 mm x 0,180 mm

9197 Kupfersäulen: 20 µm hoch, 30 µm und 60 µm Durchmesser

Panel: 610 mm x 457 mm

Leitung des Anwendungsbeispiels:

Sandvik Mining and Construction Oy

Projektpartner:

AT&S, Beneq, Besi AT, Besi NL, E+E, IMEC, InnoSent, ITE, IUNET, LGE, LUAS, MCL, PacTech, Qplox, Quantavis, RTU, SAF Tehnika, SSH, Tampere University und TU Chemnitz.

Das Projekt wurde ermöglicht durch Mittel der ECSEL-Verbundinitiative anhand Fördervereinbarung 876362. ECSEL wird durch das EU-Innovationsprogramm Horizon 2020 sowie die Mitgliedstaaten Belgien, Deutschland, Finnland, Italien, Lettland, die Niederlande, Österreich, Polen, die Schweiz und Tschechien unterstützt.

Projektwebsite

»Ende 2024 haben wir die »Glass Panel Technology Group« ins Leben gerufen«, erläutert Kahle und hebt damit die Möglichkeiten der Zusammenarbeit zwischen dem Fraunhofer IZM und der Industrie hervor. »Mit dieser Initiative streben wir an, glasbasierte Substrate für das Advanced Packaging zu entwickeln und deren Einsatz in der Datencentertechnologie sowie im High Performance Computing zu fördern. Unternehmen entlang der gesamten Wertschöpfungskette von Glas-Substraten sind eingeladen, sich unserer Initiative anzuschließen und gemeinsam die Glass Panel Technology voranzutreiben.«

Glas bietet aufgrund seiner materialbedingten Eigenschaften eine vielversprechende Grundlage für technologische Innovationen in der Mikroelektronik. Besonders die hohe Dimensionsstabilität ermöglicht die Herstellung von feinen Leiterbahnen mit Strukturbreiten von unter 5 μm.

Add comment