Um das exponentielle Wachstum der Rechenleistung nachhaltig zu sichern, setzt die Halbleiterindustrie verstärkt auf modulare Chiplet-Systeme. Innovative Technologien wie 3D-Heterointegration und elektrisch-optisches Co-Packaging spielen dabei eine zentrale Rolle.

Das Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM fördert die Entwicklung und Integration von Chiplet-Technologien aktiv im Rahmen der APECS-Pilotlinie. Diese wird im Zuge des EU Chips Act aufgebaut, um Chiplet-Innovationen voranzutreiben und die Forschungs- und Fertigungskapazitäten für Halbleiter in Europa zu erhöhen.

Im Interview mit Rolf Aschenbrenner und Erik Jung vom Fraunhofer IZM sowie Dr. Michael Töpper von der Forschungsfabrik Mikroelektronik Deutschland (FMD) erhalten Sie Einblicke, wie die APECS-Pilotlinie Unternehmen bei der Umsetzung fortschrittlicher Technologien im Bereich Advanced Packaging und der Integration von Chiplets unterstützt.

Können Sie bitte kurz erläutern, in welchen Bereichen das Fraunhofer IZM an der Entwicklung von Chiplet-Technologien arbeitet?

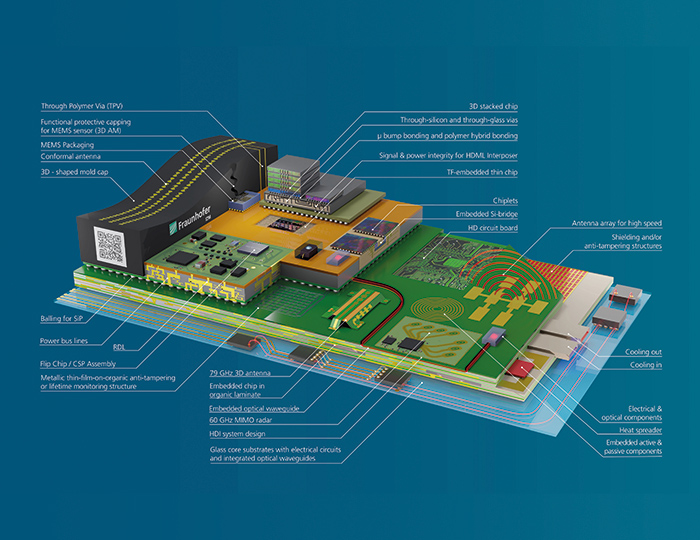

Rolf Aschenbrenner: Am Fraunhofer IZM liegt unser Schwerpunkt auf der Hardware-Integration. Mit unserem umfangreichen Technologie-Baukasten zur Hetero-Integration stellen wir Chiplet-Module her und unterstützen Systemdesign, Zuverlässigkeit und Testing.

Für welche Branchen ist eine solche technische Infrastruktur von Bedeutung?

Rolf Aschenbrenner: Die Einsatzmöglichkeiten von Chiplets sind sehr vielfältig: Überall dort, wo extrem hohe Rechenleistung und sehr hohe Integrationsdichte erforderlich sind z.B. für KI-Anwendungen im Bereich Automotive und Industrieelektronik.

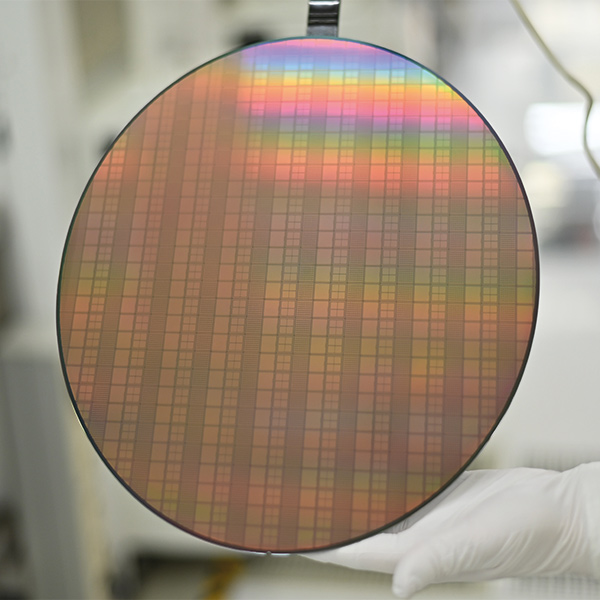

Erik Jung: Wir sehen daher den Schwerpunkt unserer Arbeit in der ganzheitlichen Systemperspektive zur Integration und Optimierung solcher Chiplet-Module. Beginnend mit dem ungehäusten Chip noch im Wafer-Verbund ergänzen wir z.B. die Metallisierung oder fügen Bumps zur Finepitch-Kontaktierung hinzu. Diesen Ansatz verfolgen wir nicht nur für die High-Performance CMOS-Chiplets, sondern adressieren auch III-V basierende RF oder optoelektronische Chiplet-Komponenten.

Ohne Hetero-Integration sind Chiplet basierte Systeme nicht möglich! Das High-End Performance Packaging vom Wafer zum System ist insoweit entscheidend für die Hardware-Realisierung und den nachhaltigen Erfolg der Chiplet-Technologie.

Technologie-Baukasten des Fraunhofer IZM: Das High-End Performance Packaging vom Wafer zum System ist einer der Schlüssel zur Hardware-Realisierung innerhalb der APECS-Pilotlinie | © Fraunhofer IZM I Mike Groß

Welchen Beitrag soll die APECS-Pilotlinie für den Standort Deutschland bzw. Europa leisten?

Michael Töpper: Die Entwicklung von Chiplets wird derzeit von großen Halbleiterunternehmen vorangetrieben, die in der Lage sind, die hohen Kosten für die Herstellung von Wafern und den damit notwendigen Masken unter 7 nm tragen zu können. Mit der APECS-Pilotlinie bieten wir Start-ups und kleinen und mittelständischen Unternehmen (KMUs), die nicht über diese Ressourcen verfügen, eine Hardware-Plattform und eröffnen Chancen für Anwendungen, die in den nächsten Jahren in den Markt kommen werden.

Rolf Aschenbrenner: Der EU Chips Act zielt darauf ab, den Anteil der Chipproduktion in Europa von derzeit 9 Prozent bis 2030 auf 20 Prozent zu erhöhen. Um Chiplet-Technologien zu integrieren und zu funktionalisieren, sind spezielles Know-how sowie Techniken für Assembly, Montage und Substrate und der Zugang zu Forschungsinfrastrukturen entscheidend.

An welche Zielgruppen richtet sich das Angebot der APECS-Pilotlinie?

Erik Jung: Die APECS-Pilotlinie richtet sich an die gesamte europäische Mikroelektronik-Industrie, von Start-ups über KMUs bis hin zu großen Unternehmen, einschließlich Zulieferern im Automotive-Bereich und Forschungseinrichtungen. Der Zugang ist für alle offen. Wir bieten eine in sich vollständige Plattform für alle Anbieter in der Wertschöpfungskette, von Foundries und Integrated Device Manufacturers (IDM) über Outsourced Semiconductor Assembly and Test (OSAT) bis hin zu Mikrosystemtechnik- und Elektronikanwendern, Ausbildungsorganisationen, Universitäten, Testhäusern und Materialherstellern.

Michael Töpper: Die APECS-Pilotlinie ist auf die Zusammenarbeit mit europäischen Institutionen konzentriert. Da die Entwicklung von Mikroelektronik jedoch länderübergreifend ist, planen wir auch Kooperationen mit Japan, Taiwan, Südkorea und den USA.

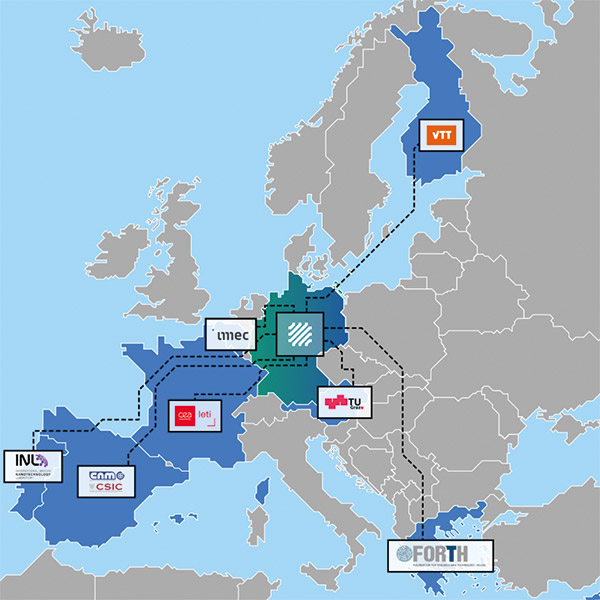

»APECS«, kurz für Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems, bringt die Kompetenzen, Infrastrukturen und das Know-how von zehn Partnern aus acht europäischen Ländern zusammen.

In Deutschland sind zwölf Institute der Fraunhofer-Gesellschaft (Projektkoordinator) und zwei Institute der Leibniz-Gemeinschaft an der Pilotlinie beteiligt. Implementiert wird APECS von der Forschungsfabrik Mikroelektronik Deutschland (FMD) – einem der weltweit führenden und standortübergreifenden Forschungs- und Entwicklungs-Zusammenschlüsse für die Mikro- und Nanoelektronik.

Welchen Mehrwert wird die APECS-Pilotlinie der Halbleiterindustrie bieten?

Erik Jung: Mit der APECS-Pilotlinie schaffen wir eine Brücke zwischen Forschung und industrieller Umsetzung. Die Partner an den Pilotlinien entwickeln gemeinsam Technologien, die für einzelne Unternehmen oft zu komplex, zeit- oder kostenaufwändig sind. Ziel ist es, Partner zu befähigen, moderne Technologien für neue Konzepte zu testen, umzusetzen und ohne große Hürden in ihre Produktion zu überführen.

Dadurch erhalten Unternehmen klare Informationen darüber, welche Geräte sie für spezifische Prozesse benötigen und welche Rahmenbedingungen entscheidend sind, um die optimale Auswahl für ihr Produktportfolio zu treffen.

Michael Töpper: Anstatt zu sagen, dass etwas technisch unmöglich oder zu komplex ist, soll die APECS-Pilotlinie dazu beitragen, neue Ideen umzusetzen und neue Märkte zu erschließen. Wir möchten Forschungsinstituten, Start-ups und KMUs einen einfachen Zugang ermöglichen, um Hardware-Prototypen in Kleinstserien von mehreren hundert Stück für neue Ideen herzustellen. Am Fraunhofer IZM zeigt die Start-a-Factory bereits erfolgreich, wie das funktioniert. Mit APECS setzen wir diesen Ansatz im Bereich der Hochtechnologie um.

Es geht dabei nicht nur um Silizium-Chips, sondern auch um Hochfrequenz-Chips auf Basis von III-V-Halbleitern sowie MEMS- und optoelektronischen Komponenten. Das gesamte Konzept soll auf weitere Herstellungstechnologien in der Halbleitertechnik ausgeweitet werden.

Was unterscheidet die APECS-Pilotlinie von einer normalen Fertigungslinie?

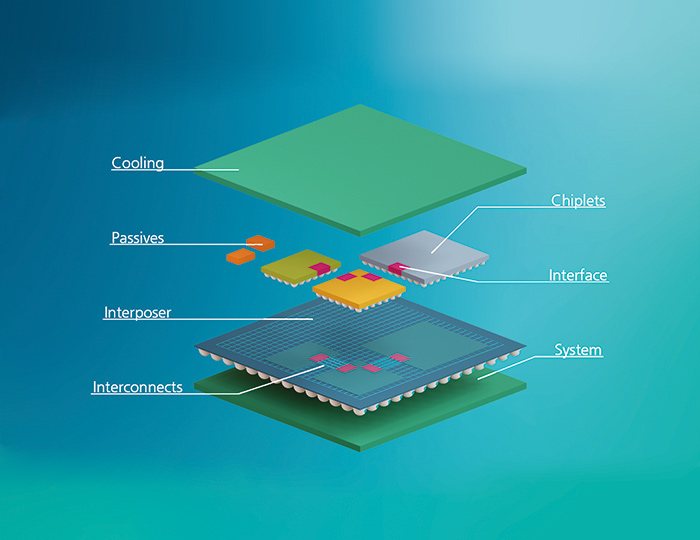

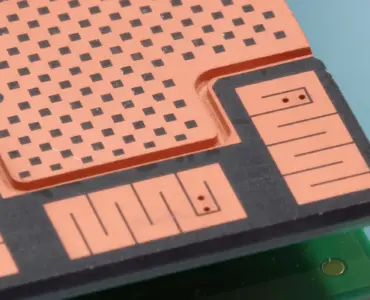

Rolf Aschenbrenner: APECS ist eine hochmoderne Forschungsinfrastruktur zur Entwicklung hochpräziser Integrationstechnologien und modularer Chiplet-Architekturen. Die Weiterentwicklung hochpräziser Integrationstechnologien (2D, 2,5D, 3D) ist unerlässlich für die Herstellung hochfunktionaler Systeme.

Für Anwendungen in der künstlichen Intelligenz und im High Performance Computing sind das Prototyping von organischen Substraten mit Strukturen bis zu 1 Mikrometer und neue Materialien wie Glas entscheidend. In den Bereichen Substrate, Assembly und Integration besteht erheblicher Forschungsbedarf, den APECS vorantreiben wird.

Die APECS-Pilotlinie ist eine von insgesamt fünf Pilotlinien, die von Chips Joint Undertaking kofinanziert werden:

Die FAMES-Pilotlinie* wird von CEA-leti in Frankreich koordiniert und konzentriert sich auf die Verbesserung der FD-SOI-Technologie (Fully Depleted Silicon on Insulator), die bei der Herstellung energieeffizienter und leistungsstarker Halbleiter zum Einsatz kommt. Zudem hat sie das Ziel, die derzeitige Transistordichte auf 7 nm zu verringern.

Unter der Leitung des imec in Belgien fokussiert die NanoIC-Pilotlinie* auf die Front-End-of-Line-Fertigung für fortgeschrittene 2-nm-Halbleiter und darunter.

Die Pilotlinie für Halbleiter mit großer Bandlücke (WBG) wird von CNR in Italien geleitet und konzentriert sich auf Werkstoffe, die die Betreibung elektronischer Geräte bei höheren Spannungen, Frequenzen und Temperaturen als herkömmliche Siliziumgeräte ermöglichen.

Die vom ICFO in Spanien koordinierte PIXEurope ist eine europäische Pilotlinie für fortgeschrittene photonische integrierte Schaltungen. Ziel ist, Europas Fähigkeiten im Bereich photonischer Chips zu stärken und die EU als weltweit führend auf diesem Gebiet zu etablieren.

*Die Fraunhofer-Gesellschaft ist Partner in den beiden Pilotlinien FAMES und NanoIC.

APECS bringt die technologischen Kompetenzen, die Infrastruktur und das Know-how von zehn Partnern aus acht europäischen Ländern zusammen. | © loewn

Wie unterscheidet sich die APECS-Pilotlinie von den anderen europäischen Pilotlinien?

Rolf Aschenbrenner: APECS wird mit der FAMES- und mit der NanoIC-Pilotlinie interagieren. Die Konsortien dieser drei Pilotlinien haben verschiedene Projekte zum Auf- und Ausbau der Zusammenarbeit definiert.

Erik Jung: Im Unterschied zur WBG-Pilotlinie, die in Tampere in Finnland komplett neu aufgebaut wird, setzt die APECS-Pilotline auf das bereits sehr umfangreiche technologische Angebot der zwölf beteiligten Fraunhofer-Institute und der beiden Leibniz-Institute FBH und IHP auf. Unter Einbeziehung vorhandener Bestandgeräte wird APECS auch dort Schlüsselinnovationen vorantreiben und den Schulterschluss mit den anderen Pilotlinien suchen.

An welchem Standort wird die APECS-Pilotlinie entstehen?

Rolf Aschenbrenner: Die Forschungsinfrastruktur wird sich dezentral auf verschiedene Standorte der Fraunhofer-Gesellschaft verteilen. Ein Fertigungssteuerungssystem (Manufacturing Execution System, MES) wird den kompletten Durchlauf und Transport von Chips und Wafern zwischen den beteiligten Einrichtungen sicherstellen.

Worin besteht der Vorteil einer dezentral über verschiedenen Orten angelegten Pilotlinie?

Michael Töpper: Ein großer Vorteil ist die Möglichkeit, unterschiedliche Materialien anwenden zu können, da nicht alle wie z.B. Gold in einem Reinraum verarbeitet werden können. Darüber hinaus ist jedes Fraunhofer-Institut und jedes Leibniz-Institut eng mit ein oder mehreren universitären Einrichtung verknüpft, was zu einem weiteren erheblichen wissenschaftlichen Impuls für die Forschung beiträgt, da lokale Exzellenzkompetenzen hinzugezogen werden können.

Inwiefern wird das Fraunhofer IZM an der Pilotlinie beteiligt sein?

Rolf Aschenbrenner: Das Fraunhofer IZM wird an den zwei Standorten in Dresden und Berlin an der Pilotlinie beteiligt sein. Wobei in Dresden neben dem Fraunhofer IZM-ASSID auch das Fraunhofer IPMS, beide als 300 mm-Standorte, Teil der APECS-Pilotlinie ist. Zudem sind auch die in Sachsen ansässigen Institute Fraunhofer ENAS und Fraunhofer IIS-EAS beteiligt.

Erik Jung: Nicht zu unterschätzen ist, dass auch die Region Berlin mit etwa 50 Millionen Euro für den Aufbau neuer Infrastruktur unterstützt wird, die sich nahtlos in die bestehende Expertise in der Region einbinden wird. Mit der APECS-Pilotlinie werden wir eine neue Qualität und Quantität zur Förderung der in Europa ansässigen Mikroelektronikindustrie bereitstellen.

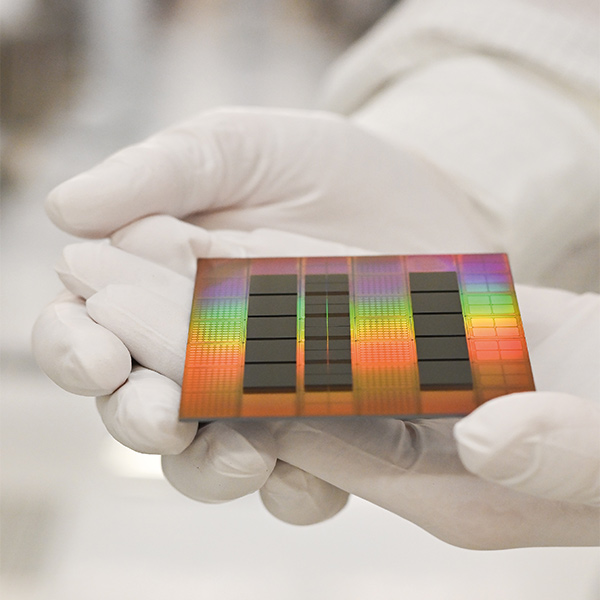

Rolf Aschenbrenner: Am Fraunhofer IZM in Berlin und am Fraunhofer IZM-ASSID in Dresden bauen wir eine Infrastruktur für Interposer-Technologien auf – sei es Silizium, Organik und Glas auf 200 mm Wafern sowie auf 300 mm Wafern und Paneln auf Organik. Ein Angebot in dieser Form und Vielfalt ist bisher einzigartig weltweit.

Mit dem neu gegründeten Chiplet Center of Excellence (CCoE) in Dresden wollen wir gemeinsam mit dem Fraunhofer IIS/EAS und Fraunhofer ENAS neue Maßstäbe für die Automobil-Elektronik setzen.

Von links nach rechts:

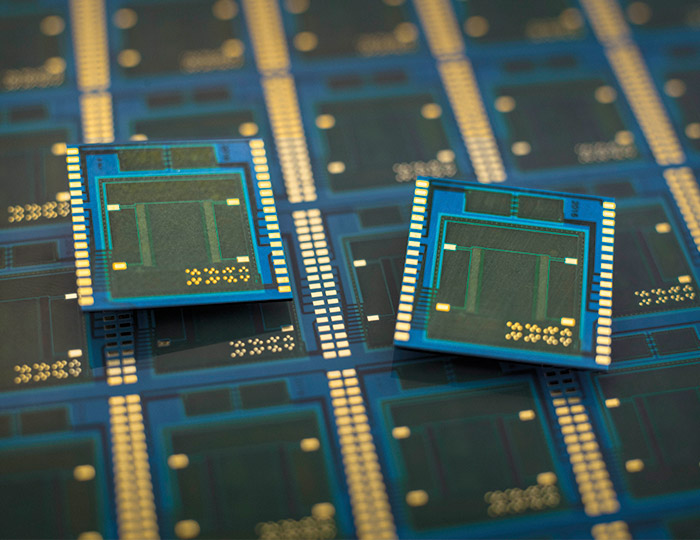

Multi-Chip Stapel mit Mikrobumps als Verbindungselement | © Fraunhofer IZM I Volker Mai

Advanced Fan-Out Wafer- und Panel-Packaging auf der Basis von Embedded-Technologien | © Fraunhofer IZM I Volker Mai

Demonstrator: 300 mm Si-Wafer mit hochdichten Kupfer-Verbindungen für die Chiplet-Integration im Rahmen des Projekts »T4T« Copyright | © Fraunhofer IZM-ASSID, Silvia Wolf

Demonstrator: Montierte Chiplets mit ultra-feinen Kupfer-Hybridbondkontakten auf einem Pitch von 10 µm | © Fraunhofer IZM-ASSID, Silvia Wolf

Erik Jung: Neben den High Performance Computing (HPC) und KI-Clustern sind auch Einsatzszenarien denkbar, bei denen mit Unterstützung von Künstlicher Intelligenz die Datenverarbeitung direkt auf dem Sensorknoten (Edge AI) – also direkt am Ort der Datenerhebung – stattfindet.

Denkbar wäre, dass in der Industrieelektronik eine komplexe Bildverarbeitung direkt auf dem Sensorknoten erfolgt. Hochintegrierte Chiplets in einer optimierten Zusammenstellung aus Computing, Energieversorgung, Drahtlostechnologien können hier zu einem »Gamechanger« werden.

Michael Töpper: Auf der Consumer Electronics Show (CES) in Las Vegas wurden Anfang des Jahres erstmals Fernsehgeräte vorgestellt, die KI-gestützte automatische Übersetzungen bieten. Künstliche Intelligenz wird in allen Branchen neue Anwendungen schaffen. Im Maschinenbau beispielsweise wird KI in Kombination mit Objekterkennung außergewöhnliche Möglichkeiten schaffen.

Wann wird die APECS-Pilotlinie einsatzfähig sein?

Michael Töpper: Es bestehen bereits jetzt Möglichkeiten der Zusammenarbeit, die im Zug der Erweiterung auf ein höheres technologisches Level gebracht werden. Erste Anfragen liegen uns bereits vor.

Welche Möglichkeiten der Zusammenarbeit bietet die Pilotlinie den Akteuren in Deutschland und Europa?

Rolf Aschenbrenner: Der Eintrittspunkt für die Zusammenarbeit mit der APECS-Pilotlinie kann vielfältig sein. Die APECS-Pilotlinie unterstützt grundsätzlich die Entwicklung eines ganzheitlichen Systemdesigns und vermittelt Prozessverständnis. Dies umfasst die Definition der Chiplet-Schnittstellen, die Herstellung von Substraten sowie Zuverlässigkeitstests und die Fertigung eines kompletten Chiplet-Moduls.

In der Regel haben Unternehmen bereits einen Ansatz zur Umsetzung eines Chiplet-Moduls, benötigen jedoch Unterstützung bei der Entwicklung eines organischen Interposers. In diesem Fall wäre der Einstiegspunkt ein Projekt mit uns am Fraunhofer IZM in der APECS-Pilotlinie, um einen organischen Interposer für Chiplets zu realisieren und ein funktionsfähiges Chiplet-Modul herzustellen.

Erik Jung: Unternehmen könnten auch Schulungen für modernste Prozesse erhalten, Auftragsforschung anfragen oder exklusive Pilotfertigungen von Kleinserien durchführen. Die APECS-Pilotlinie bietet europäischen Partnern für solche Szenarien maßgeschneiderte Zugangsmodelle und Lösungen an.

Michael Töpper: Ich möchte hervorheben, dass uns die Verbindung zum Chipdesign wichtig ist. Wir fokussieren uns nicht nur auf die Technologie, sondern verfolgen mit APECS auch den Ansatz der System-Technology-Co-Optimization (STCO). Es ist uns wichtig, das Chipdesign eng mit der Technologie zusammenzubringen, um realisierbare Lösungen zu schaffen und den Chipdesigner*innen zugleich neue Möglichkeiten zu eröffnen.

Welche Rolle spielt die Geschäftsstelle der Forschungsfabrik Mikroelektronik Deutschland (FMD) beim Aufbau der APECS-Pilotlinie?

Michael Töpper: Die FMD-Geschäftsstelle agiert vielseitig: Wir übernehmen das gesamte Projektmanagement und die Vermarktung, koordinieren den Geräteeinkauf und leiten die Entwicklung der Demonstratoren. Zudem sind wir die zentrale Schnittstelle zu den Projektträgern auf deutscher und europäischer Ebene und fungieren als »Matchmaker« für die europäische Halbleitertechnik.

Sie haben gerade die Entwicklung von Demonstratoren angesprochen. Was konkret ist geplant?

Michael Töpper: Zur Demonstration der Funktionsfähigkeit der APECS-Pilotlinie werden vier Demonstratoren entwickelt, die verschiedene Bereiche des technologischen Portfolios abdecken: Hochfrequenztechnik, Opto-Elektronik, High Performance Computing und die Integration von MEMS-Technologie.

An wen und in welcher Form können sich Interessenten wenden?

Michael Töpper: Unser Expert*innen-Team ist vor Ort in Berlin und jederzeit auch per E-Mail unter experts@mikroelektronik.fraunhofer.de erreichbar. Wir bringen die Interessenten sehr schnell mit den jeweiligen Ansprechpartner*innen aus unserem Netzwerk zusammen. Uns ist wichtig, Anfragen kundenorientiert zu beantworten. Bei Bedarf begleiten wir diese auch. Die Erstellung der Angebote und deren Realisierung obliegt jedoch unseren Partnern wie beispielsweise dem Fraunhofer IZM.

Müssen Interessenten beim Erstkontakt bestimmte Kriterien beachten z.B. ein Pitch Deck mitsenden?

Michael Töpper: Es gibt keinen formalen Prozess oder vorgefertigte Lösungen; der Schlüssel liegt im Gespräch. Im Austausch mit unseren Fachexpert*innen wird für Kunden oft klarer, was sie wirklich benötigen und welche zusätzlichen Aspekte, wie beim Chipdesign, zu berücksichtigen sind. Mit unseren Beratungsleistungen bieten wir maßgeschneiderte Lösungsansätze an.

Vereinfachte Darstellung einer Chiplet-Architektur © Fraunhofer IIS

Wie Erik Jung bereits erwähnt hat, können wir oft schon mit kleineren Aktivitäten, wie Fortbildungen, entscheidend weiterhelfen. Ein Beispiel könnte ein dreistündiger Workshop sein, in dem Fachexpert*innen erläutern, was genau hinter dem Begriff »Chiplet« steckt.

Welche Meilensteine stehen 2025 auf der Agenda der FMD-Geschäftsstelle?

Michael Töpper: Unsere Kernaufgabe für 2025 ist, das Serviceangebot der APECS-Pilotlinie sichtbar zu machen und die Managementstruktur aufzubauen. Wir werden in diesem Jahr die Pilotlinie auf ausgewählten Konferenzen und Messen wie z.B. der Sensor+Test in Nürnberg, EuMW in Utrecht und SEMICON EUROPE in München präsentieren.

Ein weiteres wichtiges Ziel ist es, den Austausch mit den bereits im Konsortium und im Projekt engagierten Partnern zu intensivieren. Gemeinsam bilden wir die APECS-Pilotlinie, und unsere Aufgabe ist es, diese zum Laufen zu bringen.

Vielen Dank für das Gespräch!

Koordinierung: Fraunhofer-Gesellschaft

Durchführung: Forschungsfabrik Mikroelektronik Deutschland (FMD)

Projektpartner (national): zwölf Institute des Fraunhofer-Verbunds Mikroelektronik und zwei Leibniz-Institute FBH und IHP

Projektpartner (europäisch): TU Graz, VTT, imec, CEA-Leti, FORTH, IMB-CNM-CSIC, INL

Laufzeit: 1.11.2024 bis 30.06.2029

Förderung: Das Vorhaben wurde im Rahmen der APECS-Pilotlinie durch Chips

Joint Undertaking (das durch Horizon Europe und Digital Europe Programme gefördert wird) und durch nationale Förderungen von Belgien, Deutschland, Finnland, Frankreich, Griechenland, Österreich, Portugal und Spanien kofinanziert.

Weitere Informationen: APECS-Webseite und APECS-LinkedIn

Add comment